RMx System On Module Specification

In commercial confidence.

This document and its contents are the property of Blue Chip Technology from whom permission must be sought for any reproduction of its contents. Whilst every effort is made to ensure accuracy, no liability can be assumed for errors or omissions.

# CONTENTS

| CONTENTS                                   | 2  |

|--------------------------------------------|----|

| INTRODUCTION                               | 4  |

| COMPATIBILITY                              | 4  |

| MODULE OVERVIEW                            | 5  |

| INTERFACE PIN SUMMARY                      | 6  |

| SIGNAL/PIN DEFINITIONS                     |    |

| Power                                      |    |

| Example current levels                     |    |

| LCD INTERFACE                              |    |

| SLOW SERIAL INTERFACES                     |    |

| I <sup>2</sup> C INTERFACES                |    |

| GPIO                                       |    |

| USB                                        |    |

| TV                                         |    |

| Audio                                      |    |

| VIDEO/CAMERA INTERFACES                    |    |

| LAN/Ethernet                               |    |

| SATA                                       |    |

| DVI/HDMI                                   |    |

| PCIE                                       |    |

| SDIO/SD/MMC<br>Key Notes for Compatibility |    |

| EXPANSION BUS                              |    |

| MISCELLANEOUS                              |    |

| MECHANICAL SPECIFICATION                   |    |

| APPENDIX A – WORKING WITH RM2              |    |

| POWER                                      |    |

| LCD INTERFACE                              |    |

| I <sup>2</sup> C INTERFACES                |    |

| GPIO                                       |    |

| USB                                        |    |

| TV                                         | 21 |

| Audio                                      |    |

| Video / Camera Interface                   |    |

| LAN / ETHERNET                             |    |

| SDIO/SD/MMC                                |    |

| EXPANSION BUS                              |    |

| Miscellaneous                              |    |

|                                            |    |

| APPENDIX B – WORKING WITH RM3 |  |

|-------------------------------|--|

| POWER                         |  |

| LCD INTERFACE                 |  |

| I <sup>2</sup> C INTERFACES   |  |

| GPIO                          |  |

| USB                           |  |

| AUDIO                         |  |

| VIDEO / CAMERA INTERFACE      |  |

| LAN / Ethernet                |  |

| SATA                          |  |

| HDMI / DVI                    |  |

| PCI Express                   |  |

| SDIO/SD/MMC                   |  |

| EXPANSION BUS                 |  |

| MISCELLANEOUS                 |  |

| DOCUMENT HISTORY              |  |

| REFERENCES                    |  |

# INTRODUCTION

This document details the physical and electrical interfaces for Blue Chip Technology 'RMx' System On Module (SOM) Products.

The RMx SOM product range is an ARM-based set of compact, processing modules designed for embedded control and media applications, and the host interfaces are designed to maximise re-use. A host platform designed for one SOM should be able to implement the same functionality using a different SOM with little or no adaptation.

# COMPATIBILITY

Note that – unlike PC platform interface standards – System On Modules are designed to implement as much functionality as is practical 'on-card' (to keep host board design simple), and so it is not always possible or practical to use fully-standardised interfaces. As a few examples:-

The SOM interface provides a basic wired Ethernet interface, which is implemented with the PHY on the SOM: this leaves the interface magnetics and final connector on the host board. Whilst it is possible to use the same magnetics with a range of PHY devices and accept the resulting trade-offs, it would be better to select a design which can offer a family of solutions in the same package so that a host board could be easily optimised for a range of PHY devices.

The SOM interface provides connections to enable extension of an on-card bus to enable devices on the host board to be close-coupled to the SOM processor. Whilst fairly simple devices can be supported from the SOM range, more complex implementations which are designed to take advantage of a particular processor may prove less tolerant of SOM changes. The host board designer has the option to either 'keep it simple' to improve cross-SOM compatibility, or tailor for a particular SOM/SOM family to gain a performance advantage or to enable functionality which couldn't otherwise be supported.

Interfaces and device mapping will always be a function of the main processing engine in use. Software should always abstract the main hardware layer in order to make porting between platforms easier.

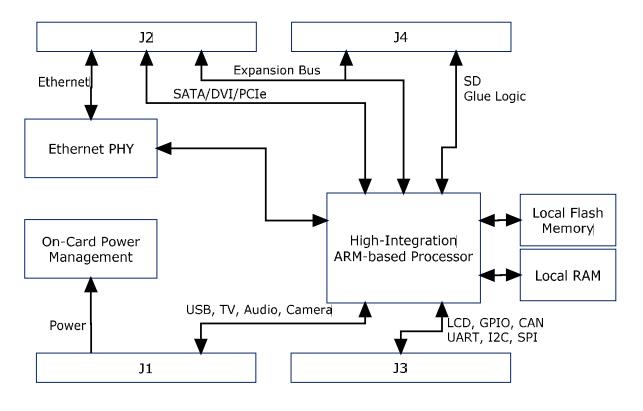

# **MODULE OVERVIEW**

The Blue Chip Technology RMx SOM is a compact module designed for use with a variety of carrier boards. It provides a rage of interfaces and functionality as indicated in the block diagram below. Actual interfaces and functionality varies with SOM module, but all use the same PCB header interconnect, and so suitably-designed carrier/host boards can work with a range of SOM modules.

**SOM Block Diagram**

## **INTERFACE PIN SUMMARY**

In the following pin summaries, currently 'reserved' pins are greyed out. Host boards should not make connections to these pins without first consulting with Blue Chip Technology. Not all RMx SOM PCBs support all of the defined pins

| LCD | GND          | 2 1   | GND       | CAMERA    |

|-----|--------------|-------|-----------|-----------|

|     | LCD_D14      | 4 3   |           |           |

|     | LCD_D15      | 6 5   |           |           |

|     | GND          | 8 7   |           |           |

|     | LCD_D16      | 10 9  |           | SLOW      |

|     | LCD_D17      | 12 11 | _         | SERIAL    |

|     | _<br>LCD_D18 | 14 13 | _         |           |

|     | LCD_D19      | 16 15 |           |           |

|     | LCD_D20      | 18 17 | UARTB_TX  |           |

|     | LCD_D21      | 20 19 | _         |           |

|     | GND          | 22 21 | _         |           |

|     | LCD_D22      | 24 23 | _         |           |

|     | LCD_D23      | 26 25 | GND       |           |

|     | LCD_PCLK     | 28 27 | SPI_CLK   |           |

|     | GND          | 30 29 | SPI_CSB   |           |

|     | LCD_HSYNC    | 32 31 | SPI_SIMO  |           |

|     | LCD_VSYNC    | 34 33 | SPI_SOMI  |           |

|     | LCD_DE       | 36 35 | SPI_CSA   |           |

|     | LCD_D0       | 38 37 | SOM_IRQA# | INTERRUPT |

|     | LCD_D1       | 40 39 | SOM_IRQB# |           |

|     | LCD_D2       | 42 41 | GND       |           |

|     | LCD_D3       | 44 43 | I2CA_SCL  | I2C       |

|     | GND          | 46 45 | I2CA_SDA  |           |

|     | LCD_D4       | 48 47 | I2CB_SCL  |           |

|     | LCD_D5       | 50 49 | I2CB_SDA  |           |

|     | LCD_D6       | 52 51 | GPIO1     | GPIO      |

|     | LCD_D7       | 54 53 | GPIO2     |           |

|     | LCD_D8       | 56 55 | GPIO3     |           |

|     | LCD_D9       | 58 57 | GPIO4     | _         |

|     | GND          | 60 59 | GND       |           |

|     | LCD_D10      | 62 61 | GPIO5     |           |

|     | LCD_D11      | 64 63 | GPIO6     |           |

|     | LCD_D12      | 66 65 | GPIO7     |           |

|     | LCD_D13      | 68 67 | GPIO8     |           |

|     | GND          | 70 69 | GND       |           |

J3

| LCD   | LCD_ENA        | 2    | 1  | GND              | CAMERA |

|-------|----------------|------|----|------------------|--------|

| CNTRL | LCD_BL_ENA     | 4    | 3  | CAM_XD3          |        |

|       | <br>GND        | 6    | 5  | CAM_XD2          |        |

| USB   | USB_HOST_P     | 8    | 7  | CAM_XD1          |        |

| ноѕт  | USB_HOST_N     | 10   | 9  | _<br>CAM_XD0     |        |

|       | GND            | 12 1 | 1  | CAM_D9           |        |

|       | USB_DEV_P      | 14 1 | 13 | CAM_D8           |        |

|       | USB_DEV_N      | 16 1 | ۱5 | CAM_D7           |        |

|       | GND            | 18 1 | 17 | CAM_D6           |        |

| POWER | VCC5           | 20 1 | 19 | GND              |        |

|       | VIO            | 22 2 | 21 | CAM_D5           |        |

|       | VIO            | 24 2 | 23 | CAM_D4           |        |

| TV    | GND            | 26 2 | 25 | CAM_D3           |        |

|       | TV_LUMA_COMP   | 28 2 | 27 | CAM_D2           |        |

|       | GND            | 30 2 | 29 | CAM_D1           |        |

|       | TV_CHROMA      | 32 3 | 31 | CAM_D0           |        |

|       | GND            | 34 3 | 33 | GND              |        |

| LCD   | LCD_PWMB       | 36 3 | 35 | CAM_STROBE       |        |

| PWM   | LCD_PWMA       | 38 3 | 37 | CAM_WEN          |        |

|       | GND            | 40 3 | 39 | CAM_FLD          |        |

| AUDIO | AUD_LINEIN_L   | 42 4 | 11 | CAM_HS           |        |

|       | AUD_LINEIN_R   | 44 4 | 13 | CAM_VS           |        |

|       | AUD_MICIN_BIAS | 46 4 | 15 | GND              |        |

|       | AUD_MICIN_N    | 48 4 | 17 | CAM_PCLK         |        |

|       | AUD_MICIN_P    | 50 4 | 19 | GND              |        |

|       | GND            | 52 5 | 51 | CAM_XCLKB        |        |

|       | AUD_LINEOUT_R  | 54 5 | 53 | CAM_XCLKA        |        |

|       | AUD_LINEOUT_L  | 56 5 | 55 | GND              |        |

|       | GND            | 58 5 | 57 | CAM_GLOBAL_RESET |        |

|       | IIS_DX         | 60 5 | 59 | GND              |        |

|       | IIS_DR         | 62 6 | 51 | 3V3_SBY          | POWER  |

|       | IIS_CLKX       | 64 6 | 53 | VCC3_3           |        |

|       | IIS_FSX        | 66 6 | 55 | VCC3_3           |        |

|       | AUDIORSTN      | 68 6 | 57 | VCC3_3           |        |

|       | GND            | 70 6 | 59 | VCC3_3           |        |

J1

| LAN  | GND          | 2            | 1 | GND          |      |

|------|--------------|--------------|---|--------------|------|

| 2.00 | ETH_TX2_P    |              |   | EXPN_CEO#    |      |

|      | ETH_TX2_N    |              |   | EXPN_CE1#    |      |

|      | GND          |              |   | GND          | SATA |

|      | ETH_RX2_P    |              |   | SATA_RX_N    | -    |

|      | ETH_RX2_N    | 12 12        |   | SATA_RX_P    |      |

|      | GND          | 14 13        |   | GND          |      |

|      | ETH_TX1_P    | 16 1         |   | SATA_TX_N    |      |

|      | ETH_TX1_N    | 18 17        |   | SATA_TX_P    |      |

|      | GND          | 20 19        |   | GND          | DVI  |

|      | ETH_RX1_P    | 22 23        | 1 | HDMI_C_N     |      |

|      | ETH_RX1_N    | 24 23        |   | HDMI_C_P     |      |

|      | GND          | 26 25        | 5 | GND          |      |

|      | ETH_SPD_LED# | 28 27        | 7 | HDMI_D2_N    |      |

|      | ETH_LNK_LED# | 30 29        | 9 | HDMI_D2_P    |      |

|      | ETH_CTT      | 32 33        | 1 | GND          |      |

|      | GND          | 34 33        | 3 | HDMI_D1_N    |      |

| BUS  | EXPN_WP#     | 36 35        | 5 | HDMI_D1_P    |      |

| EXPN | EXPN_CE4#    | 38 37        | 7 | GND          |      |

|      | EXPN_WE#     | 40 39        | 9 | HDMI_D0_N    |      |

|      | EXPN_RE#     | 42 42        | 1 | HDMI_D0_P    |      |

|      | EXPN_ALE     | 44 43        | 3 | GND          |      |

|      | EXPN_A11     | 46 45        | 5 |              |      |

|      | EXPN_READY   | 48 47        | 7 |              |      |

|      | EXPN_A7      | 50 49        | 9 | GND          |      |

|      | EXPN_A6      | <b>52</b> 52 | 1 | PCIE_CLK_P   | PCle |

|      | EXPN_A5      | 54 53        | 3 | PCIE_CLK_N   |      |

|      | EXPN_A4      | 56 55        | 5 | GND          |      |

|      | EXPN_A3      | 58 57        | 7 | PCIE_TX_P    |      |

|      | EXPN_A2      | 60 59        | 9 | PCIE_TX_N    |      |

|      | EXPN_A1      | 62 63        |   | GND          |      |

|      | EXPN_D15     | 64 63        |   | PCIE_RX_P    |      |

|      | EXPN_D14     | 66 65        |   | PCIE_RX_N    |      |

|      | EXPN_D13     | 68 67        |   | GND          |      |

|      | GND          | 70 69        | 9 | USB_DEV_VBUS |      |

J2

| BUSEXPN_FLASH_SEL443EXPNEXPN_D10260.50.0000.000[Continued]EXPN_D101100.0000.0000.000EXPN_D102120.0000.0000.0000.000EXPN_D203120.0000.0000.0000.000EXPN_D204120.0000.0000.0000.000EXPN_D205200.0000.0000.0000.000EXPN_D205200.0000.0000.0000.000EXPN_D205200.0000.0000.0000.000EXPN_D205200.0000.0000.0000.000EXPN_D205200.0000.0000.0000.000EXPN_D205200.0000.0000.0000.000MISCGPI01034300.0000.0000.000MISCGPI01034300.0000.0000.000MISCGPI01034300.0000.0000.000MISCGPI01034300.0000.0000.000MISCGPI01034300.0000.0000.000MISCGPI01034300.0000.0000.000MISCGPI01034300.0000.0000.000MISCGPI01034300.0000.0000.000GEXPN_CIC323030300.000GEXPN_CIC30 <t< th=""><th></th><th></th><th>2</th><th>1</th><th>GND</th><th></th></t<> |             |                 | 2  | 1  | GND       |        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|----|----|-----------|--------|

| EXPN  EXPN_D12  6  5    [Continued]  EXPN_D11  8  7    EXPN_D10  10  9  GND    EXPN_D20  12  11    EXPN_D3  14  13    EXPN_D6  18  17    EXPN_D5  20  19    EXPN_D4  22  21    EXPN_D5  20  19    EXPN_D5  24  23    EXPN_D1  28  27    EXPN_D1  28  27    EXPN_D1  28  27    MISC  GPI010  34  33    YCC3_3  YCC3_3                                                                                                                                                                                                                                                                                                                                                                                                            | DUC         | GND             | 2  |    | GND       |        |

| [Continued]EXPN_D1087EXPN_D101096NDEXPN_D191211EXPN_D281413EXPN_D71615EXPN_D52019EXPN_D42221EXPN_D5209EXPN_D22625EXPN_D12827EXPN_D12331MISCGPI0103433MISCGPI0103433YS_RESWARM#3837YS_RESWARM#38302_041WAKEUP#4440BOOT_MODE#4443SU_DATA3SD/MMCGPI094840SOM_RC2#5050_DATA3SOM_RC2#5050_DATA3SOM_RC2#5050_LOATA3SDM_RC2#5050_LOATA3SD1_W5851_COGRI06261_DATA3SD1_WF5850_LOATA3SD1_WF5850_LOATA3SD1_WF5850_LOATA3SD1_WF5850_LOATA3SD1_WF5850_LOATA3SD1_WF6463SD1_DATA264HDMI_HPD62GFI050_LOATA3SUS_GTG_D68SD1_OATA350_LOATA3                                                                                                                                                                                                        |             |                 |    |    |           |        |

| EXPN_D1010GNDEXPN_D31211EXPN_D81413EXPN_D71615EXPN_D61817EXPN_D7209EXPN_D32221EXPN_D32423EXPN_D42221EXPN_D52625EXPN_D12827EXPN_D12827EXPN_D12824EXPN_D33231MISCGPI003433VCC3_3VCC3_3MISCGPI0103433VCC3_3VCC3_3WAKEUP#4030MISCGPI0134BOOT_MODE#4443SYS_RESWARM#38302_DATA1GPI034847SOM_RC#50_DATA2GPI0448502_OATA3SOM_RC#50501_COWIRELESS_PVREN5251SD1_WP58501_COGRI036050_DATA2GN50_DATA2GN50_DATA3GN50_DATA3GN50_DATA3GN50_DATA3GN50_DATA3GN50_DATA2GN50_DATA2GN61GN60GN50_DATA3GN50_DATA3GN50_DATA3GN50_DATA3GN50_DATA3GN50_DATA3GN50_DATA3GN                                                                                                                                                                                 |             | _               |    |    |           |        |

| EXPN_D8  12  11    EXPN_D8  14  13    EXPN_D7  16  15    EXPN_D6  18  17    EXPN_D5  20  19    EXPN_D4  22  21    GND  26  25    EXPN_D0  30  29    EXPN_D0  30  29    MISC  GPI010  34  33    YCC3_3  VCC3_3  VCC3_3    MISC  GPI010  34  33    YSS_RESWARM#  38  37  VCC3_3    WAKEUP#  40  39  SD/MMC    BOOT_MODE#  44  32  DATA1    BOOT_MODE#  44  32  DATA1    GPI09  48  47  SD_DATA2    GPI09  48  47  SD_DATA3    GPI09  48  47  SD_DATA3    GPI09  48  50  SD_CATA3    GPI09  48  50  SD_LATA3    GNM_RCQ  50  SD_LATA3  SOM_IAQU    GNM_RCQ <t< td=""><td>[Continued]</td><td>_</td><td></td><td></td><td></td><td></td></t<>                                                                                       | [Continued] | _               |    |    |           |        |

| EXPN_D81413EXPN_D71615EXPN_D61817EXPN_D52019EXPN_D42221EXPN_D52625EXPN_D12827EXPN_D03029EXPN_D03231MISCGPI0103433PSON3635SYS_RESWARM#3837VCC3_3VCC3_3WAKEUP#4030BOOT_MODE#4443SOM_IRQC#50502_DATA0SOM_IRQC#50502_DATA3SOM_IRQC#50502_CMDWIRELESS_PWR_EN5251SD1_WP5857SD1_WP58501SD1_WP6261SD1_WP6261HDMI_HPD6261GE6151_DATA1USB_OTG_D6867SD1_DATA3501_OATA1                                                                                                                                                                                                                                                                                                                                                                     |             | _               |    |    | GND       |        |

| EXPN_DG1615EXPN_DG1817EXPN_D52019EXPN_D42221EXPN_D32423EXPN_D22626EXPN_D03029EXPN_D03029MISCGPIO1034PSON3635YSS_RESWARM#3837VCC3_3YCC3_3WAKEUP#4030EXPN_C1E4241BOOT_MODE#4443BOOT_MODE#4443BOOT_MODE#4845SOM_IRQC#5050_ZCMDWIRELESS_PWR_EN5252_DATA3SOM_IRQC#50_QCMD14WIRELESS_PWR_EN52_CIKSOM_IRQC#50_LCNMIRC6050SD1_WP5850SD1_WP6261SD1_WP6251_DATA0HDMI_HPD6261SD_DATA214SD1_WP6350_LATA1SD1_WP6350_LATA1SD1_WP6351_DATA3                                                                                                                                                                                                                                                                                                    |             | _               |    |    |           |        |

| EXPN_DG1817EXPN_D52019EXPN_D42221EXPN_D32423EXPN_D122626EXPN_D03029CMMD2433MISCGPI0103433PSON3636SYS_RESWARM#3870WAKEUP#4030WAKEUP#43302_DATA1BOOT_MODE#44302_DATA2BOOT_MODE#44302_DATA2GND5254SOM_IRQC#50502_CMDWIRELESS_PWR_EN5251SOM_IRQC#54502_CMDWIRELESS_PWR_EN5251SD1_WP5851MID6051_DATA0HDMI_HPD6261GI6151_DATA1USB_OTG_ID6861_DATA3                                                                                                                                                                                                                                                                                                                                                                                    |             | -               |    |    |           |        |

| EXPN_D42090EXPN_D422GNDEXPN_D32423EXPN_D22625EXPN_D03029EXPN_D03231MISCGPI0103433PSON3635SYS_RESWARM#3870WAKEUP#40302_DATA0WAKEUP#44302_DATA1BOOT_MODE#4443BOOT_MODE#4443GND502_DATA2GND IRQC#502_DATA3SOM_IRQC#502_CMDSOM_IRQC#502_CMDWIRELESS_PWR_EN52SD1_CD58SD1_CD60HDMI_HPD62GRID501_DATA1USB_OTG_ID68SD1_DATA3USB_OTG_ID68SD1_DATA3                                                                                                                                                                                                                                                                                                                                                                                       |             | _               |    |    |           |        |

| EXPN_D422GNDEXPN_D324CAEXPN_D226CAEXPN_D128CAEXPN_D030C2EXPN_D032VCC3_3MISCGPI01034VCC3_3PSON36VCC3_3SYS_RESWARM#38VCC3_3WAKEUP#40SD_DATA0WAKEUP#44SD2_DATA0BOOT_MODE#44SD2_DATA1CAM_IRQ64SD2_DATA3GPI0948SD2_DATA3WIRELESS_PWRENSC2_CMDSOM_IRQC#S0SD2_CMDWIRELESS_PWRENSC2_CMDSD1_CDSD1_OATA3SD1_WPSASD1_CDHDMI_HPD62SD1_DATA1HDMI_HPD62SD1_DATA1HDMI_HPD64SD1_DATA3USB_OTG_ID68SD1_DATA3                                                                                                                                                                                                                                                                                                                                      |             | _               |    |    |           |        |

| EXPN_D2242424EXPN_D22625EXPN_D12827EXPN_D03029MISCGPI0103432PSON363233SYS_RESWARM#3837VCC3_3WAKEUP#4030GNDWAKEUP#4443SD2_DATA0BOOT_MODE#4443SD2_DATA1BOOT_MODE#4443SD2_DATA3GRIO50/MMC50/MMC50/MMCBOOT_MODE#4847SD2_DATA1GRIO50SD2_CMD100WIRELESS_PWR_EN5251SD2_CMDSOM_IRQ#5450SD1WIRELESS_PWR_EN5251SD1_WP5851SD1_WP6151_DATA0HDMI_HPD6261HDMI_HPD6251_DATA1HDMI_HPD6251_DATA1LGCE6461S1_DATA2LGCE6461S1_DATA3LGCE6651_DATA3LGCE6651_DATA3                                                                                                                                                                                                                                                                                     |             |                 |    |    |           |        |

| EXPN_D<br>EXPN_D12625EXPN_D03029MSCGPI0103231MSCGPI0103433SYS_RESWARM#387VCC3_3VCC3_3WAKEUP#4030MSCEXPN_CLE22MAKEUP#4432DOT_MODE#4432AGDT_MODE#48ASD2_DATA0SD/MMCGRIO4832MIRELESS_PWR_EN5252SOM_IRQ#5052WIRELESS_PWR_EN5252SD1_WP5851SD1_WP5851HDMI_HPD6261HDMI_HPD6251_DATA1HDMI_HPD6861SD_DATA3SI_LATA1LISB_OTG_ID6861SD1_WF5351_DATA3                                                                                                                                                                                                                                                                                                                                                                                        |             |                 |    |    | GND       |        |

| EXPN_D2827EXPN_D03029MISCGPI0103231VCC3_3VCC3_3PSON3635SYS_RESWARM#387WAKEUP#4030WAKEUP#42502_DATA0BOOT_MODE#4440_DATA0BOOT_MODE#44502_DATA1CAM_IRQ6050_DATA2SOM_IRQC#50_OATA3WIRELESS_PWR_EN52_CATASOM_IRQC#50_DATA3WIRELESS_PWR_EN52_CATASD1_WP5850_LOATA0SD1_WP6050_DATA1HDMI_HPD6260_DATA1HDMI_HPD6250_DATA1GRO50_DATA1GRO6050_DATA1GRO6050_DATA1GRO6050_DATA1GRO6050_DATA1GRO6050_DATA1GRO6360_DATA1GRO6460_DATA1GRO6460_DATA3GRO6460_DATA3GRO6460_DATA3GRO6650_DATA3GRO6860_DATA3GRO6860_DATA3                                                                                                                                                                                                                            |             | _               |    |    |           |        |

| EXPN_03029MISCGPIO103231VCC3_3MISCGPIO103433VCC3_3SYS_RESWARM#3837VCC3_3WAKEUP#4039GNDWAKEUP#4241SD2_DATA0BOOT_MODE#4443SD2_DATA1CAM_IRQ4645SD2_DATA2GPIO94847SD2_DATA3WIRELESS_PWR_EN5251SD2_CKKWIRELESS_PWR_EN5251SD1_CCSD1_WP5852SD1SD1_WP5851SD1_CATA0HDMI_HPD6261SD1_DATA0USB_OTG_ID6867SD1_DATA3                                                                                                                                                                                                                                                                                                                                                                                                                          |             | _               |    |    |           |        |

| MISCGPIO1032VCC3_3MISCGPIO1034VCC3_3PSON36SCC3_3SYS_RESWARM#38VCC3_3WAKEUP#40GNDWAKEUP#42SD2_DATA0BOOT_MODE#44SD2_DATA1BOOT_MODE#44SD2_DATA1CAM_IRQ66SD2_DATA3GPIO948SD2_CMDWIRELESS_PWR_ENSD2_CLKSOM_IRQC#SODWIRELESS_PWR_ENSD2_CLKEXPN_RESET#SO1_DATA0SD1_WPS3SD1_CDSD1_WP53SD1_CDHDMI_HPD62SD1_DATA1HDMI_HPD62SD1_DATA1LGE64SD1_DATA2USB_OTG_ID68SD1_CMD                                                                                                                                                                                                                                                                                                                                                                     |             |                 |    |    |           |        |

| MISC  GPI010  34  33  VCC3_3    PSON  36  35  VCC3_3    SYS_RESWARM#  38  37  VCC3_3    WAKEUP#  40  39  GND    EXPN_CLE  42  41  SD2_DATA0  SD/MMC    BOOT_MODE#  44  43  SD2_DATA1  SD    CAM_IRQ  46  45  SD2_DATA2  SD    GPI09  48  47  SD2_DATA3  SD    SOM_IRQC#  50  49  SD_CMD  SD    WIRELESS_PWR_EN  52  51  SD_CLK  SD    EXPN_RESET#  54  53  GND  SD  SD    SD1_WP  58  57  SD1_CD  SD                                                                                                                                                                                |             |                 | 30 | 29 |           |        |

| PSON3635VCC3_3SYS_RESWARM#3837VCC3_3WAKEUP#4039GNDEXPN_CLE4241SD2_DATA0BOOT_MODE#4443SD2_DATA1CAM_IRQ4645SD2_DATA2GPIO94847SD2_DATA3SOM_IRQC#5049SD2_CMDWIRELESS_PWR_EN5251SD2_CLKEXPN_RESET#5453GNDVBATT5650VSD1SD1_WP5857SD1_CDMIDH_HPD6261SD1_DATA0HDMI_HPD6261SD1_DATA1CEC6463SD1_DATA3USB_OTG_ID6867SD1_CMD                                                                                                                                                                                                                                                                                                                                                                                                                |             | GND             | 32 | 31 | VCC3_3    |        |

| SYS_RESWARM#  38  37  VCC3_3    WAKEUP#  40  39  GND    EXPN_CLE  42  41  SD2_DATA0  SD/MMC    BOOT_MODE#  44  43  SD2_DATA1  SD4_MARA    CAM_IRQ  46  45  SD2_DATA2  SD4_MARA    GPIO9  48  47  SD2_DATA3  SD4_MARA    SOM_IRQC#  50  49  SD2_CMD  SD4_MARA    WIRELESS_PWR_EN  52  51  SD2_CLK  SD4_MARA    SD1_WP_RESET#  54  53  GND  SD4_MARA    SD1_WP  58  57  SD1_CD  SD4_MARA    HDMI_HPD  62  61  SD1_DATA0  SD4_MARA    LUSB_OTG_ID  68  67  SD1_DATA3  SD4_MARA                                                                                                                                                                                                                                                     | MISC        | GPIO10          | 34 | 33 | VCC3_3    |        |

| WAKEUP#  40  39  GND    EXPN_CLE  42  41  SD2_DATA0  SD/MMC    BOOT_MODE#  44  43  SD2_DATA1    CAM_IRQ  46  45  SD2_DATA2    GPI09  48  47  SD2_DATA3    SOM_IRQC#  50  49  SD2_CMD    WIRELESS_PWR_EN  52  50  SD1    EXPN_RESET#  54  50  SD1    VBATT  56  SD1  SD1    SD1_WP  58  51  SD1_CD    HDMI_HPD  62  61  SD1_DATA0    HDMI_HPD  62  61  SD1_DATA1    CEC  64  63  SD1_DATA2    USB_OTG_ID  68  67  SD1_MARA                                                                                                                                                                                                                                                                                                       |             | PSON            | 36 | 35 |           |        |

| EXPN_CLE  42  41  SD2_DATA0  SD/MMC    BOOT_MODE#  44  43  SD2_DATA1    CAM_IRQ  46  45  SD2_DATA2    GPIO9  48  47  SD2_DATA3    SOM_IRQC#  50  49  SD2_CMD    WIRELESS_PWR_EN  52  51  SD2_CLK    EXPN_RESET#  54  50  SD1    SD1_WP  56  SD1  SD1    SD1_WP  58  57  SD1_CD    HDMI_HPD  62  61  SD1_DATA0    HDMI_HPD  62  61  SD1_DATA1    CEC  64  63  SD1_DATA2    USB_OTG_ID  68  67  SD1_CMD                                                                                                                                                                                                                                                                                                                           |             | SYS_RESWARM#    | 38 | 37 | VCC3_3    |        |

| BOOT_MODE#  44  43  SD2_DATA1    CAM_IRQ  46  45  SD2_DATA2    GPIO9  48  47  SD2_DATA3    SOM_IRQC#  50  49  SD2_CMD    WIRELESS_PWR_EN  52  51  SD2_CLK    EXPN_RESET#  54  53  GND    SD1_WP  56  SD1_CD    SD1_WP  58  51  SD1_CD    HDMI_HPD  62  61  SD1_DATA0    CEC  64  63  SD1_DATA1    USB_OTG_ID  68  67  SD1_CMD                                                                                                                                                                                                                                                                                                                                                                                                   |             | WAKEUP#         | 40 | 39 | GND       |        |

| CAM_IRQ  46  45  SD2_DATA2    GPIO9  48  47  SD2_DATA3    SOM_IRQC#  50  49  SD2_CMD    WIRELESS_PWR_EN  52  51  SD2_CLK    EXPN_RESET#  54  53  GND    VBATT  56  55  VSD1    SD1_WP  58  57  SD1_DATA0    HDM1_HPD  62  61  SD1_DATA1    CEC  64  63  SD1_DATA2    MSB_OTG_ID  68  67  SD1_CMD                                                                                                                                                                                                                                                                                                                                                                                                                                |             | EXPN_CLE        | 42 | 41 | SD2_DATA0 | SD/MMC |

| GPIO9  48  47  SD2_DATA3    SOM_IRQC#  50  49  SD2_CMD    WIRELESS_PWR_EN  52  51  SD2_CLK    EXPN_RESET#  54  53  GND    VBATT  56  55  VSD1    SD1_WP  58  57  SD1_DATA0    HDMI_HPD  62  61  SD1_DATA1    CEC  64  63  SD1_DATA2    USB_OTG_ID  68  67  SD1_CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             | BOOT_MODE#      | 44 | 43 | SD2_DATA1 |        |

| SOM_IRQC#  50  49  SD2_CMD    WIRELESS_PWR_EN  52  51  SD2_CLK    EXPN_RESET#  54  53  GND    VBATT  56  55  VSD1    SD1_WP  58  57  SD1_CD    MDMI_HPD  60  59  SD1_DATA0    HDMI_HPD  62  61  SD1_DATA1    CEC  64  63  SD1_DATA2    USB_OTG_ID  68  67  SD1_CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             | CAM_IRQ         | 46 | 45 | SD2_DATA2 |        |

| WIRELESS_PWR_EN52SD2_CLKEXPN_RESET#5450VBATT56VSD1SD1_WP58SD1_CDGND6050HDMI_HPD62SD1_DATA0CEC64SD1_DATA2USB_OTG_ID6867SD1_CMDSD1_CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             | GPIO9           | 48 | 47 | SD2_DATA3 |        |

| EXPN_RESET#5453GNDVBATT5655VSD1SD1_WP5857SD1_CDGND6059SD1_DATA0HDMI_HPD6261SD1_DATA1CEC6463SD1_DATA2USB_OTG_ID6867SD1_CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             | SOM_IRQC#       | 50 | 49 | SD2_CMD   |        |

| VBATT    56    VSD1      SD1_WP    58    57    SD1_CD      GND    60    59    SD1_DATA0      HDMI_HPD    62    61    SD1_DATA1      CEC    64    63    SD1_DATA2      USB_OTG_ID    68    67    SD1_CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             | WIRELESS_PWR_EN | 52 | 51 | SD2_CLK   |        |

| SD1_WP  58  57  SD1_CD    GND  60  59  SD1_DATA0    HDMI_HPD  62  61  SD1_DATA1    CEC  64  63  SD1_DATA2    USB_OTG_ID  68  67  SD1_CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             | EXPN_RESET#     | 54 | 53 | GND       |        |

| GND  60  59  SD1_DATA0    HDMI_HPD  62  61  SD1_DATA1    CEC  64  63  SD1_DATA2    USB_OTG_ID  68  67  SD1_CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             | VBATT           | 56 | 55 | VSD1      |        |

| HDMI_HPD  62  61  SD1_DATA1    CEC  64  63  SD1_DATA2    0  66  65  SD1_DATA3    USB_OTG_ID  68  67  SD1_CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             | SD1_WP          | 58 | 57 | SD1_CD    |        |

| CEC  64  63  SD1_DATA2    66  65  SD1_DATA3    USB_OTG_ID  68  67  SD1_CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             | GND             | 60 | 59 | SD1_DATA0 |        |

| CEC  64  63  SD1_DATA2    66  65  SD1_DATA3    USB_OTG_ID  68  67  SD1_CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             | HDMI_HPD        | 62 | 61 |           |        |

| USB_OTG_ID 68 67 SD1_CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             | CEC             | 64 | 63 |           |        |

| USB_OTG_ID 68 67 SD1_CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |                 | 66 | 65 | SD1_DATA3 |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             | USB_OTG_ID      |    | 67 |           |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             | <br>GND         | 70 | 69 |           |        |

J4

Note that the signal names used above are generic for all RMx modules. Each RMx module has an appendix including a description of how these generic signal names map onto the specific signal names used by each processor manufacturer.

## **SIGNAL/PIN DEFINITIONS**

All directions are given with respect to the host/carrier board (ie: 'O' or 'Output' is a signal from the host board to the SOM).

[NB: See the latest revision for up-to-date listings of SOM units, and for allocations of any previously 'reserved'pins].

### POWER

| Power   | Pin   | Power Rail  | Description:                         | Availability: |

|---------|-------|-------------|--------------------------------------|---------------|

|         | Type: | /Tolerance: |                                      |               |

| VCC3_3  | PWR   | 3.3V        | Power feed for SOM                   | RM2/RM3       |

| 3V3_SBY | PWR   | 3.3V        | Standby power feed for SOM           | RM2/RM3       |

| VIO     | PWR   | 1.8V(typ)   | Power reference from SOM             | RM2/RM3       |

|         |       | 3.3V (max)  |                                      |               |

| VCC5    | PWR   | 5V          | Power feed for SOM                   | RM2/RM3       |

| VBATT   | PWR   | 1.8V-3.3V   | Nom 3V (1.8V-3.3V) DC power feed for | RM2/RM3       |

|         |       |             | SOM RTC                              |               |

| GND     | PWR   | 0V          | Power/signal ground                  | RM2/RM3       |

VIO is a reference supply provided by the RMx SOM to identify the configured logic level for a number of interfaces. For flexible support of RMx SOMs, this should be used to define the SOM side of a level-shifter for affected circuits. It is possible to operate without a level-shifter if a host platform is designed for a specific RMx SOM (in which case the I/O voltage can be designed against that provided in the specific RMx documentation).

It is recommended that host boards are able to support powering as in the table below to support the range of RMx SOMs anticipated. It is possible to reduce power levels based on the specific RMx modules targeted, but note that: a) figures are for the RMx only (additional power will be required for the host board and I/O interfaces; b) it is generally a good practice to allow a good margin on top of nominal figures to ensure power-up stability & reliability over life.

Provision of VBATT is optional (note that maintaining the RTC in power down may not be possible if this supply is not available). Typical drain in powered-off modes depends on implementation.

3V3\_SBY is required, and should always be present whenever the other main supplies (VCC5 & VCC3\_3) are available.

#### Example current levels

| Rail:   | Nominal<br>Voltage: | Current<br>(RM2): | Current<br>(RM3): |  | Recommended<br>Supply: |

|---------|---------------------|-------------------|-------------------|--|------------------------|

| 3V3_SBY | 3.3V                | 0.1A              | TBA               |  | 0.2A                   |

| VCC3_3  | 3.3V                | 1A                | TBA               |  | 4A                     |

| VCC5    | 5V                  | 0.1A              | TBA               |  | 1A                     |

### LCD INTERFACE

| Digital Display #1<br>(Parallel/LCD) | Pin<br>Tuna | Power Rail<br>/Tolerance: | Description:                      | Availability: |

|--------------------------------------|-------------|---------------------------|-----------------------------------|---------------|

|                                      | Type:       |                           |                                   |               |

| LCD_D0                               | 1           | VIO                       | 24-bit parallel display interface | RM2/RM3       |

| LCD_D23                              | Ι           |                           |                                   | RM2/RM3       |

| LCD_HSYNC                            | Ι           |                           | Horizontal synchronisation        | RM2/RM3       |

| LCD_VSYNC                            | Ι           |                           | Vertical synchronisation          | RM2/RM3       |

| LCD PCLK                             | Ι           |                           |                                   | RM2/RM3       |

| LCD_DE                               | Ι           |                           |                                   | RM2/RM3       |

| LCD_ENA                              | Ι           | VIO                       | Enable/disable panel              | RM2/RM3       |

| LCD_BL_ENA                           | Ι           |                           | Enable/disable backlight          | RM2/RM3       |

| PWM Output | Pin<br>Type: | Power Rail<br>/Tolerance: | Description:                 | Availability: |

|------------|--------------|---------------------------|------------------------------|---------------|

| LCD_PWMA   | Ι            | 3.3V                      | Pulse-width modulator output | RM2/RM3       |

| LCD_PWMB   | Ι            |                           | Pulse-width modulator output | RM2/RM3       |

[If not required for brightness/contrast control, the PWM outputs can be used as general-purpose PWM outputs].

The LCD interface is designed for simple connection of panels offering a basic, parallel interface. Backlight/inverter power should be provided by the host PCB.

#### **SLOW SERIAL INTERFACES**

| CAN   | Pin<br>Type: | Power Rail<br>/Tolerance: | Description:     | Availability: |

|-------|--------------|---------------------------|------------------|---------------|

| CAN 1 | 0            | 3.3V                      | RX (to SOM)      | RM3           |

| CAN_2 | Ι            |                           | TX (from SOM)    | RM3           |

| CAN_3 | Ι            |                           | TX_EN (from SOM) | RM3           |

The CAN transceiver is implemented on the host PCB when required.

| UART A     | Pin   | Power Rail  | Description:            | Availability: |

|------------|-------|-------------|-------------------------|---------------|

|            | Type: | /Tolerance: |                         |               |

| UARTA_TX   | Ι     | 3.3V        | Serial transmit         | RM2/RM3       |

| UARTA_ENTX | Ι     |             | Transmit enable control | RM2/RM3       |

| UARTA_RX   | 0     |             | Serial receive          | RM2/RM3       |

| UART B   | Pin<br>Type: | Power Rail<br>/Tolerance: | Description:    | Availability: |

|----------|--------------|---------------------------|-----------------|---------------|

| UARTB_TX | I            | 3.3V                      | Serial transmit | RM2/RM3       |

| UARTB_RX | O            |                           | Serial receive  | RM2/RM3       |

Two, simple, two-wire UART interfaces are provided at basic logic level. UARTA adds a transmit enable signal to simplify use on multi-drop buses (eg: RS485) where disabling/tristating of the transceiver is required. Handshaking and access control, if desired, should be implemented at the software level (eg: using 'XON/XOFF').

UARTB is the default debug serial port. It is recommended that this be made available (as a minimum as contactable pads, or a pin header interface) on host boards.

| SPI      | Pin<br>Type: | Power Rail<br>/Tolerance: | Description: | Availability: |

|----------|--------------|---------------------------|--------------|---------------|

| SPI_CLK  | Ι            | 3.3V                      |              | RM2/RM3       |

| SPI CSB  | Ι            |                           |              | RM2/RM3       |

| SPI_SIMO | Ι            |                           |              | RM2/RM3       |

| SPI_SOMI | 0            |                           |              | RM2/RM3       |

| SPI_CSA  | Ι            |                           |              | RM2/RM3       |

The Serial Peripheral Interface bus provided by the SOM operates with the SOM as master, and up to two slave addresses attached (selected using SPI\_CSA & SPI\_CSB) operating in independent mode. Note that – if two devices are used on this bus, both must be capable of operating in multi-slave environments (ie: must support 'slave select' signalling and tri-state outputs when not addressed).

# I<sup>2</sup>C INTERFACES

| I <sup>2</sup> C | Pin<br>Type: | Power Rail<br>/Tolerance: | Description: | Availability: |

|------------------|--------------|---------------------------|--------------|---------------|

| I2CA SCL         | I/O          | 5V                        |              | RM2/RM3       |

| I2CA SDA         | I/O          | 5V                        |              | RM2/RM3       |

| I2CB SCL         | I/O          | 3.3V                      |              | RM2/RM3       |

| I2CB_SDA         | I/O          | 3.3V                      |              | RM2/RM3       |

I2CA is the default for use as a DDC channel for a display interface (see later).

#### GPIO

| GPIO   | Pin<br>Type: | Power Rail<br>/Tolerance: | Description:                           | Availability: |

|--------|--------------|---------------------------|----------------------------------------|---------------|

| GPIO1  | Ι            | 3.3V                      | General purpose I/O signals            | RM2/RM3       |

| GPIO2  | Ι            |                           |                                        | RM2/RM3       |

| GPIO3  | Ι            |                           |                                        | RM2/RM3       |

| GPIO4  | Ι            |                           |                                        | RM2/RM3       |

| GPIO5  | 0            |                           |                                        | RM2/RM3       |

| GPIO6  | 0            |                           |                                        | RM2/RM3       |

| GPIO7  | 0            |                           |                                        | RM2/RM3       |

| GPIO8  | 0            |                           |                                        | RM2/RM3       |

| GPIO9  | Ι            |                           | Often used for Bluetooth power enable. | RM2/RM3       |

| GPIO10 | 0            |                           |                                        | RM3           |

The direction of each GPIO interface indicated above is supported by all RMx SOMs. Some RMx SOMs may offer more flexibility (see specific documentation for capabilities).

#### USB

| USB Device   | Pin<br>Type:       | Power Rail<br>/Tolerance: | Description:                                         | Availability: |

|--------------|--------------------|---------------------------|------------------------------------------------------|---------------|

| USB_DEV_P/N  | I/O <sub>BAL</sub> |                           | Standard balanced USB bi-directional signal data bus | RM2/RM3       |

| USB_DEV_VBUS | А                  | 5V                        | Used to determine mode (*1)                          | RM2/RM3       |

| USB_OTG_ID   | 0                  | 5V                        | Standard USB OTG ID signal                           | RM3           |

[Note \*1: The 'USB\_DEV\_VBUS' signal on the USB device interface is fed to the SOM to indicate presence of a suitable USB 'host' on the link].

The USB Device port is a principal interface for configuration of SOM modules. It is recommended that it be made available (at least as contactable pads, or a pin header) on host boards.

The "device" port may also support OTG functionality on some modules.

| USB Host #1  | Pin<br>Type:       | Power Rail<br>/Tolerance: | Description:                                         | Availability: |

|--------------|--------------------|---------------------------|------------------------------------------------------|---------------|

| USB_HOST_P/N | I/O <sub>BAL</sub> |                           | Standard balanced USB bi-directional signal data bus | RM2/RM3       |

TV

| TV Display                | Pin<br>Type:                     | Power Rail<br>/Tolerance: | Description:    | Availability: |

|---------------------------|----------------------------------|---------------------------|-----------------|---------------|

| TV_CHROMA<br>TV_LUMA_COMP | I <sub>A</sub><br>I <sub>A</sub> |                           | S-Video signals | RM2<br>RM2    |

TV out is not available on all RMx products.

#### AUDIO

| Digital Audio | Pin<br>Type: | Power Rail<br>/Tolerance: | Description:                       | Availability:         |

|---------------|--------------|---------------------------|------------------------------------|-----------------------|

| AUDIORSTN     | Ι            | VIO                       | Reset signal for host audio codecs | RM2/RM3 <sup>*1</sup> |

| IIS_FSX       | Ι            | VIO                       | Framing for output channel         | RM2/RM3 <sup>*1</sup> |

| IIS CLKX      | Ι            | VIO                       | Transmit/receive clock             | RM2/RM3 <sup>*1</sup> |

| IIS DR        | 0            | VIO                       | Receive data                       | RM2/RM3 <sup>*1</sup> |

| IIS_DX        | Ι            | VIO                       | Transmit data                      | RM2/RM3 <sup>*1</sup> |

| Analogue Audio                               | Pin<br>Type:                                   | Power Rail<br>/Tolerance: | Description:                          | Availability:                                                           |

|----------------------------------------------|------------------------------------------------|---------------------------|---------------------------------------|-------------------------------------------------------------------------|

| AUD_LINEOUT_L                                | I <sub>A</sub>                                 | 3.3V                      | Left & right channel analogue signals | RM2/RM3 <sup>*1</sup>                                                   |

| AUD_LINEOUT_R                                | I <sub>A</sub>                                 | 3.3V                      |                                       | RM2/RM3 <sup>*1</sup>                                                   |

| AUD_MICIN_P<br>AUD_MICIN_N<br>AUD_MICIN_BIAS | $\begin{array}{c} O_A\\ O_A\\ I_A \end{array}$ | 3.3V<br>3.3V<br>3.3V      | Balanced microphone analogue signal   | RM2/RM3 <sup>*1</sup><br>RM2/RM3 <sup>*1</sup><br>RM2/RM3 <sup>*1</sup> |

| AUD_LINEIN_L                                 | O <sub>A</sub>                                 | 3.3V                      | Left line input ('mono in' for RM2)   | RM2/RM3 <sup>*1</sup>                                                   |

| AUD_LINEIN_R                                 | O <sub>A</sub>                                 | 3.3V                      | Right line input                      | RM3 <sup>*1</sup>                                                       |

Note \*1: RM3 supports either digital or analogue audio. Selection is under software control. The 'AUDIORSTN' signal will be permanently active from RM3 whilst software selection is of the on-board codec (thus holding any host-board codec in hard-reset until it is enabled to avoid possible contention on the I2C & IIS buses).

The analogue audio channel provides signal levels typically up to 0dBu (0.775V rms).

AUD\_MICIN\_BIAS is a configurable, low-voltage bias voltage to power suitable microphones.

[Note that only a mono 'line in' channel is supported on RM2].

| Digital Video In #1 | Pin   | Power Rail  | Description:                | Availability: |

|---------------------|-------|-------------|-----------------------------|---------------|

|                     | Type: | /Tolerance: |                             |               |

| CAM_GLOBAL_RESET    | Ι     | VIO         |                             | RM2/RM3       |

| CAM_XCLKA           | Ι     | VIO         |                             | RM2           |

| CAM_XCLKB           | Ι     | VIO         |                             | RM2           |

| CAM_PCLK            | 0     | VIO         | Pixel clock                 | RM2/RM3       |

| CAM_VS              | 0     | VIO         | Vertical Sync               | RM2/RM3       |

| CAM_HS              | 0     | VIO         | Horizontal Sync             | RM2/RM3       |

| CAM_FLD             | 0     | VIO         | Interleave frame indication | RM2           |

| CAM_WEN             | Ι     | VIO         | Enable camera function      | RM2/RM3       |

| CAM_STROBE          | Ι     | VIO         | Controls camera light/flash | RM2/RM3       |

| CAM_D0 - CAM_D9     | 0     | VIO         | 10-bit parallel data        | RM2/RM3       |

| CAM_XD0 - CAM_XD1   | 0     | VIO         | Function depends on module  | RM2/RM3       |

| CAM_XD2 - CAM_XD5   | 0     | VIO         |                             | RM3           |

#### **VIDEO/CAMERA INTERFACES**

The primary Digital Video Input #1 is designed for connection of cameras and similar devices to the SOM.

For maximum compatibility across modules it is recommended to use one of the following configurations:

- ITU-R BT.656 mode with 10-bit parallel data and embedded sync

- SYNC mode with 10-bit parallel data and separate Horizontal Sync and Vertical Sync

Other configurations are available, depending on which module is being used - see appendices for more information.

#### LAN/ETHERNET

| Ethernet     | Pin<br>Type: | Power Rail<br>/Tolerance: | Description:                         | Availability: |

|--------------|--------------|---------------------------|--------------------------------------|---------------|

| ETH_SPD_LED# | Ι            | 3.3V                      | Open drain driver for "Speed" LED    | RM2/RM3       |

| ETH_LNK_LED# | Ι            | 3.3V                      | Open drain driver for "Link" LED     | RM2/RM3       |

| ETH_CTT      | Α            |                           | Centre-tap connection from magnetics | RM2/RM3       |

| ETH TX1 P/N  | BAL          |                           | Transmit pair for 10/100Base-T       | RM2/RM3       |

| ETH_RX1_P/N  | BAL          |                           | Receive pair for 10/100Base-T        | RM2/RM3       |

| ETH_TX2_P/N  | BAL          |                           |                                      | RM3           |

| ETH_RX2_P/N  | BAL          |                           | Extra pairs for 1000Base-T           | RM3           |

All SOMs support a basic 10/100Base-T Ethernet configuration; some support Gigabit Ethernet.

The PHY is implemented on the SOM; magnetics and connectorisation are required on the host board.

#### SATA

| SATA        | Pin<br>Type:     | Power Rail<br>/Tolerance: | Description: | Availability: |

|-------------|------------------|---------------------------|--------------|---------------|

| SATA_RX_P/N | O <sub>BAL</sub> |                           |              | RM3           |

| SATA_TX_P/N | I <sub>BAL</sub> |                           |              | RM3           |

### DVI/HDMI

| Digital Display #2 | Pin              | Power Rail  | Description:                         | Availability: |

|--------------------|------------------|-------------|--------------------------------------|---------------|

| (DVI/HDMI)         | Type:            | /Tolerance: |                                      |               |

| HDMI_C_P/N         | I <sub>BAL</sub> | 3.3V        | DVI-I (HDMI 1.4a support may also be | RM3           |

| HDMI_D0_P/N        | I <sub>BAL</sub> |             | available) interface                 | RM3           |

| HDMI_D1_P/N        | I <sub>BAL</sub> |             |                                      | RM3           |

| HDMI_D2_P/N        | I <sub>BAL</sub> |             |                                      | RM3           |

| HDMI_HPD           | 0                | 3.3V        | Hot Plug Detect signal from attached | RM3           |

|                    |                  |             | displays                             |               |

| CEC                | I/O              | 3.3V        | 'Consumer Electronics Control'       | RM3           |

|                    |                  |             | channel (for HDMI implementations)   |               |

Digital display #2 offers DVI-SL, and may optionally offer HDMI interface support<sup>1</sup>.

If a DDC channel is required, I2CA should be used.

#### PCIE

| PCI Express (x1) | Pin              | Power Rail  | Description:                          | Availability: |

|------------------|------------------|-------------|---------------------------------------|---------------|

|                  | Type:            | /Tolerance: |                                       |               |

| PCIE_CLK_P/N     | I <sub>BAL</sub> | 3.3V        | Single-channel PCI express interface  | RM3           |

| PCIE_TX_P/N      | I <sub>BAL</sub> |             | with reference clock (for any devices | RM3           |

| PCIE_RX_P/N      | O <sub>BAL</sub> |             | requiring this feature)               | RM3           |

#### SDIO/SD/MMC

These ports provide connectivity to SD/MMC memory, or to SDIO devices (such as wireless modules).

| SD/MMC/SDIO #1 | Pin   | Power Rail  | Description:                            | Availability: |

|----------------|-------|-------------|-----------------------------------------|---------------|

|                | Type: | /Tolerance: |                                         |               |

| SD1_WP         | 0     | VSD1        | Port for connection of flash memory     | RM3           |

| SD1_CD         | 0     | 3.3V        | devices or SDIO communication           | RM2/RM3       |

| SD1_DATA0      | I/O   | VSD1        | devices.                                | RM2/RM3       |

| SD1_DATA1      | I/O   | VSD1        | VSD is a voltage output from the SOM    | RM2/RM3       |

| SD1_DATA2      | I/O   | VSD1        | to define and provide the I/O power for | RM2/RM3       |

| SD1 DATA3      | I/O   | VSD1        | the interface. It can be also be turned | RM2/RM3       |

| SD1_CMD        | I/O   | VSD1        | off & on by the SOM to shutdown         | RM2/RM3       |

| SD1_CLK        | Ι     | VSD1        | attached devices or provide a hard      | RM2/RM3       |

| VSD1           | А     | [Note *1]   | reset.                                  | RM2/RM3       |

Note \*1: VSD1 is sourced from the SOM and provides power for SD1-connected devices, and the reference voltage for any associated pull-up resistors. VSD1 is nominally in the range 2.7V to 3.6V or 1.7V to 1.95V. For maximum compatibility, use SD/SDIO or uSD cards able to operate in both voltage ranges.

<sup>&</sup>lt;sup>1</sup> HDMI support may be subject to licensing

| SD/MMC/SDIO #2     | Pin   | Power Rail  | Description:                          | Availability: |

|--------------------|-------|-------------|---------------------------------------|---------------|

|                    | Type: | /Tolerance: |                                       |               |

| SD2_DATA0          | I/O   | 3.3V        | Port for connection of flash memory   | RM2/RM3       |

| SD2_DATA1          | I/O   |             | devices or SDIO communication         | RM2/RM3       |

| SD2 DATA2          | I/O   |             | devices. Note that voltage selection, | RM2/RM3       |

| SD2 DATA3          | I/O   |             | card-detection, and write-protect     | RM2/RM3       |

| SD2 <sup>CMD</sup> | I/O   |             | features are not available for this   | RM2/RM3       |

| SD2_CLK            | Ι     |             | interface                             | RM2/RM3       |

#### Key Notes for Compatibility

SD1 is primarily designed for use with SD/MMC/SDIO devices. All RMx modules support 4-bit SD/SDIO/MMC cards operating at 'higher' voltage levels (typically 2.7V to 3.6V); not all RMx modules support switching to lower voltage mode (1.7V to 1.95V), but all support power cycling to enable card reset. Mechanical 'Write Protect' is not supported by all RMx cards.

SD2 is available for SD/MMC/SDIO type devices, but does not support any power control features or mechanical card detect/write protect. It is more appropriate for use as an interface to embedded devices on the host board.

For maximum compatibility, SD/SDIO or uSD devices are recommended.

The power supply should be decoupled at the card slot to minimise hot-insertion transients. Values of 47uF for SD cards, and 100uF for SDIO cards are recommended.

| Expansion Bus | Pin<br>Turn cu | Power Rail<br>/Tolerance: | Description:                          | Availability: |

|---------------|----------------|---------------------------|---------------------------------------|---------------|

| EXPN A11      | <i>Type:</i>   | VIO                       |                                       | RM2/RM3       |

| EXPN A7       | I              | 10                        |                                       | RM2/RM3       |

| EXPN A6       | I              |                           |                                       | RM2/RM3       |

| EXPN A5       | I              |                           |                                       | RM2/RM3       |

| EXPN A4       | I              |                           |                                       | RM2/RM3       |

| EXPN A3       | I              |                           |                                       | RM2/RM3       |

| EXPN A2       | I              |                           |                                       | RM2/RM3       |

| EXPN A1       | I              |                           |                                       | RM2/RM3       |

| EXPN D15      | I/O            |                           | 16-bit wide data bus                  | RM2/RM3       |

| EXPN D14      | I/O            |                           |                                       | RM2/RM3       |

| EXPN D13      | I/O            |                           |                                       | RM2/RM3       |

| EXPN D12      | I/O            |                           |                                       | RM2/RM3       |

| EXPN D11      | I/O            |                           |                                       | RM2/RM3       |

| EXPN D10      | I/O            |                           |                                       | RM2/RM3       |

| EXPN D9       | I/O            |                           |                                       | RM2/RM3       |

| EXPN D8       | I/O            |                           |                                       | RM2/RM3       |

| EXPN_D7       | I/O            |                           |                                       | RM2/RM3       |

| EXPN D6       | I/O            |                           |                                       | RM2/RM3       |

| EXPN_D5       | I/O            |                           |                                       | RM2/RM3       |

| EXPN_D4       | I/O            |                           |                                       | RM2/RM3       |

| EXPN_D3       | I/O            |                           |                                       | RM2/RM3       |

| EXPN_D2       | I/O            |                           |                                       | RM2/RM3       |

| EXPN_D1       | I/O            |                           |                                       | RM2/RM3       |

| EXPN_D0       | I/O            |                           |                                       | RM2/RM3       |

| EXPN_CE0#     | Ι              |                           | Three available chip-select signals.  | RM2/RM3       |

| EXPN_CE1#     | Ι              |                           | Note that some RMx modules may        | RM2/RM3       |

| EXPN_CE4#     | Ι              |                           | have restrictions on the use of these | RM2/RM3       |

| EXPN_WP#      | Ι              |                           | Write Protect                         | RM2           |

#### **EXPANSION BUS**

| Expansion Bus | Pin   | Power Rail  | Description:                          | Availability: |

|---------------|-------|-------------|---------------------------------------|---------------|

|               | Type: | /Tolerance: |                                       |               |

| EXPN_WE#      | Ι     |             | Data write strobe                     | RM2/RM3       |

| EXPN_RE#      | Ι     |             | Data read strobe                      | RM2/RM3       |

| EXPN_ALE      | Ι     |             | Address latch enable                  | RM2           |

| EXPN_READY    | Ι     |             |                                       | RM2/RM3       |

| EXPN_CLE      | Ι     |             | Command Latch Enable [NAND]           | RM2           |

| EXPN_RESET#   | Ι     |             | Can be used as a generic system reset | RM2/RM3       |

The expansion bus is provided as a flexible interface to memory-mapped host-board resources. The range available may vary dependent on RMx module in use, however there is some overlap in support.

Simple non-multiplexed devices (eg: suitably-configured FPGAs) with PSRAM/NOR flash like interfaces can be supported in order to implement specialised interface functionality.

#### MISCELLANEOUS

|                                                | Pin<br>Type:     | Power Rail<br>/Tolerance:        | Description:                                                                                                                                 | Availability:                            |

|------------------------------------------------|------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| PSON                                           | I<br>I           | 3.3V                             | Control wire from SOM<br>0 = Power off<br>1 = Power on                                                                                       | RM3                                      |

| SYS_RESWARM#                                   | 0                | [Use OD<br>driver <sup>2</sup> ] | Reset signal into SOM<br>0 = Reset RMx<br>1 = Normal operation                                                                               | RM2/RM3                                  |

| WAKEUP#                                        | 0                | [Use OD<br>driver]               | 'Wake' signal into SOM<br>0 = wake from sleep state<br>1 = [no change in state]                                                              | RM2/RM3                                  |

| BOOT_MODE#                                     | 0                | 3.3V                             | [See below]                                                                                                                                  | RM2/RM3                                  |

| WIRELESS_PWR_EN3V                              | Ι                | 3.3V                             | Control wire from SOM<br>0 = Disable WLAN<br>1 = Enable WLAN                                                                                 | RM2/RM3                                  |

| SOM_IRQA#<br>SOM_IRQB#<br>SOM_IRQC#<br>CAM_IRQ | 0<br>0<br>0<br>0 | VIO                              | Interrupt lines to SOM. 'CAM_IRQ' is<br>dedicated to the primary digital video<br>input. Pull up to VIO using 10K<br>resistors on host board | RM2/RM3<br>RM2/RM3<br>RM2/RM3<br>RM2/RM3 |

| EXPN_FLASH_SEL                                 | 0                | 5V<br>3.3V                       | [See below]                                                                                                                                  | RM2<br>RM3                               |

It is recommended that miscellaneous output pins should use open-drain drivers on the host, tolerant to 5V, in order to ensure full compatibility with all RMx modules. In practice, it is unlikely that these interfaces will be presented with more than 3.3V.

<sup>&</sup>lt;sup>2</sup> Signal is pulled up on SOM (may be to any supply between 1.8V and 5V)

Use of 'BOOT\_MODE#' and 'EXPN\_FLASH\_SEL' varies between RMx modules as indicated in the table below. These functions are intended for early development & product support purposes rather than for final product implementations.

| Signal:        | Application: | Description:                                                           |

|----------------|--------------|------------------------------------------------------------------------|

| BOOT_MODE#     | RM2          | Normal (not connected): RMx boots from on-SOM Flash.                   |

|                |              | Tied to GND: Changes the boot order to enable the module to attempt a  |

|                |              | boot from external peripherals before the on-SOM Flash memory          |

|                | RM3          | Normal (not connected): RMx boot controlled by EXPN_FLASH_SEL.         |

|                |              | Tied to GND: Force boot from USB (serial loader)                       |

| EXPN_FLASH_SEL | RM2          | Tied to GND: normal operation. The RMx boots from on-card Flash        |

|                |              | memory. The host board cannot make any connection to CS0 or CS1.       |

|                |              | Floating/pulled up: host board boot. Disables the on-SOM NAND Flash,   |

|                |              | freeing CS0 & CS1 for use on the host board. The boot NAND flash       |

|                |              | must be provisioned on the host board and connected to CS0.            |

|                | RM3          | [Only effective if BOOT_MODE# is not connected]                        |

|                |              | This pin is reserved for Blue Chip Technology use, and customers are   |

|                |              | advised to leave the pin floating (standard boot is from on-card Flash |

|                |              | memory)                                                                |

The above signals are pulled-up on the RMx (see the relevant Appendix for details), and so do not need to be pulled high on the host board in order to set a 'high' level.

BOOT\_MODE# is a dual-purpose signal intended to enable:-

- Boot from alternative interface to enable initial program/re-program of the on-SOM Flash memory

- Entry into 'engineering mode' (depending on bootloader/operating system) to enable reconfiguration of operating modes of the SOM

The former is triggered if the signal is active at power-up; the latter function is reliant on using a suitable bootloader, and is entered dependant on a software test of the same signal some time after initial power-up.

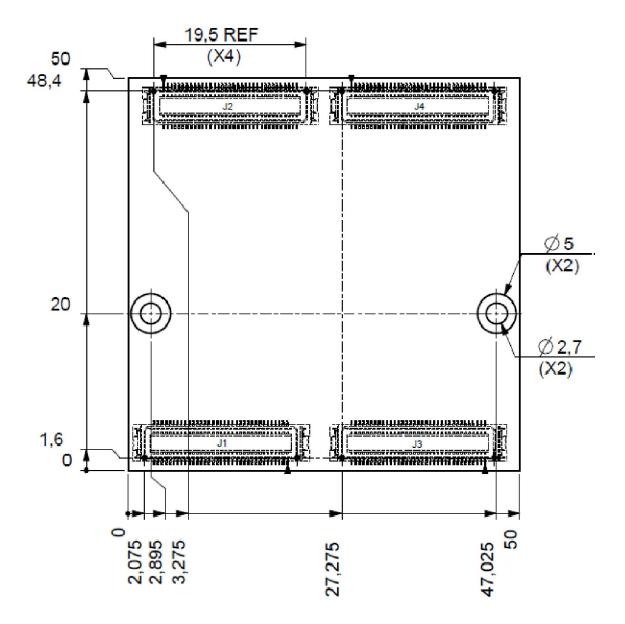

## **MECHANICAL SPECIFICATION**

Notes:-

- 1. The above shows the position of the SOM mounting sockets and outline of the SOM module as seen from the top of the PCB/host board

- 2. Pin 1 position is 'rotational': it appears top-left of sockets J2 & J4 as shown, and bottom-right of sockets J1 & J3 sockets

- 3. Polarity is ensured by the difference in spacing of the LH & RH socket pairs: it is not possible to fit the PCB incorrectly

- 4. The SOM PCB is secured in place with two mount-pillars (shown)

- 5. The connectors on the SOM module are 70-pin Hirose DF17-3.0-70DS-0.5 connectors. The mating half required on the carrier board would be the Hirose DF17-XX-70DP-0.5 where XX can be 2.0 or 2.5 or 4.0 which specifies the stacking height adjustment. With the DF17-2.0-70DS-0.5 the baseboard adds 2mm to the SOM module's 3mm to create a 5mm stacking height (between PCBs). Similarly the DF17-2.5-70DS-0.5 will create a 5.5mm stacking height; the DF17-4.0-70DS-0.5 would create a 7mm stacking height

## **APPENDIX A – WORKING WITH RM2**