## RM3 System on Module User Guide

ARM Cortex A9 System on Module

Document Reference: RM3 User Guide Document Issue: 1.4 -

# **Contents**

| Copyright                        | 3  |

|----------------------------------|----|

| Limitations of Liability         | 3  |

| Trademarks                       |    |

| Regulatory Statements            | 4  |

| Safety Warning for North America | 4  |

| Manual Organisation              | 5  |

| Introduction                     | 6  |

| Functional Overview              | 7  |

| Specification                    | 8  |

| General Precautions              | 9  |

| Electro-Static Discharges        | 9  |

| Mechanical Specifications        |    |

| Connector Details                | 11 |

| Pin Definitions                  |    |

| LCD Interface                    |    |

| Slow Serial Interfaces           |    |

| I <sup>2</sup> C Interfaces      |    |

| GPIO                             | 19 |

| USB                              |    |

| Audio                            | 19 |

| Video/Camera Interfaces          |    |

| LAN/Ethernet                     |    |

| SATA                             | 21 |

| DVI/HDMI                         | 21 |

| PCIe                             | 21 |

| SDIO/SD/MMC                      |    |

| Key Notes for Compatibility      |    |

| Expansion Bus                    |    |

| Miscellaneous                    |    |

| Cooling                          |    |

| System Software                  |    |

| Operating Systems Supported      |    |

| Maintenance                      |    |

| History                          |    |

|                                  |    |

## **Copyright**

All rights reserved. No part of this publication may be reproduced, stored in any retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopied, recorded or otherwise, without the prior permission, in writing, from the publisher. For permission in the UK please contact Blue Chip Technology.

Information offered in this manual is believed to be correct at the time of printing. Blue Chip Technology accepts no responsibility for any inaccuracies. The information contained herein is subject to change without notice. There are no express or implied licences granted herein to any intellectual property rights of Blue Chip Technology Ltd.

### **Limitations of Liability**

In no event shall Blue Chip Technology be held liable for any loss, expenses or damages of any kind whatsoever, whether direct, indirect, incidental or consequential, arising from the design or use of this product or the support materials supplied with this product. If this product proves to be defective, Blue Chip Technology is only obliged to replace or refund the purchase price at Blue Chip Technology's discretion according to their Terms and Conditions of Sale.

### **Trademarks**

All trademarks and registered names acknowledged. IBM, PC, AT and PS/2 are trademarks of International Business Machines Corporation (IBM). AMD is a registered trademark of Advanced Micro Devices Inc. MSDOS and WINDOWS are registered trademarks of the Microsoft Corporation.

### **Regulatory Statements**

CE

This product has been designed and assessed to meet the essential protection requirements of the European EMC Directive (2004/108/EC), the Low Voltage Directive (2006/95/EC), and the R&TTE Directive (1999/5/EC) when installed and used in conjunction with the guidelines provided within this document.

[Note that compliance with the R&TTE directive is only required for those versions of the product equipped with radio frequency interfaces].

FCC

NOTE:

FCC compliance of product versions equipped with radio frequency interfaces may require specific approval for the finished products.

#### WARNING:

Changes or modifications not expressly approved by the manufacturer could void the user's authority to operate the equipment.

#### **Safety Warning for North America**

If the power lead (cord) is not supplied with the computer, select a power lead according to your local electrical regulations. In the USA use a 'UL listed' lead. In Canada use a CSA approved or 'CUL listed' lead.

Si le cordon secteur n'est pas livré avec l'ordinateur, utiliser un cordon secteur en accord avec votre code electrique nationale. En l'Etat Unis utiliser un cordon secteur 'UL listed'. En Canada utiliser un cordon secteur certifié CSA, ou 'cUL listed'.

# **Manual Organisation**

This manual describes in detail the RM3 Product range.

We have tried to include as much information as possible but we have not duplicated information that is provided in the standard Technical References, unless it proved to be necessary to aid in the understanding of the product. This manual needs to be read in conjunction with the Blue Chip Technology SOM Specification Guide

The manual is sectioned as follows:

Introduction; Overviews, showing outline dimensions; Layout, showing where the various connectors are located, and their pin-out details; Firmware Setup Maintenance details

We strongly recommend that you study this manual and the other guides carefully before attempting to interface with the RM3.

If you have any suggestions as to additional information to include in the User Guide or find any errors concerning this manual or any other Blue Chip technology documentation please inform us of these, by contacting our Technical Services department with the relevant details.

# **Introduction**

The Blue Chip Technology RM3 (BCT-RM3) is based on NXP's i.MX6 Cortex A9 ARM processor and sets very high standards for integration of the processor, graphics, memory, and I/O technologies together with a unique connection system for developing your new product quickly and safely.

The RM3 is a System on Module (SOM) which follows the very successful Cortex A8 based RM2. The SOM offers the core/heart of your new product where clock speeds are extremely high, tolerances very small and termination critical. This level of technology is high and the PCB's 14 layers a testament to the complexity involved.

The BCT-RM3 is available in the following configurations:

| RM3                  | RM3-SOM-iMX6-1GHz-N[x]-T[x]          |

|----------------------|--------------------------------------|

| Example Part Number: | RM3-SOM-iMX6-1GHz-NQ-TE              |

| N[x]                 | Number of Cores: Quad: Q, Dual: D    |

| T[x]                 | Temperature: Standard (0 to 60C): S, |

|                      | Extended (-40 to 85C): E             |

The above temperatures assume sufficient cooling of the processor, so that the heat generated is not pushed back into the PCB.

All RM3s are supplied with 1GB of SDRAM and 1GB of NAND Flash. Larger capacities are possible and subject to minimum order quantities. Alternatively, further additional NAND Flash can be added through the host board (IC, SD, MMC, CF, etc), if required.

The BCT-RM3 operates from 3.3 volts and 5 volts DC. The power requirements vary depending on the CPU type and the workload. Please see the RM3 Power Requirements document for details.

To aid Hostboard development detailed schematics for reference Hostboard designs are available on request.

#### **Functional Overview**

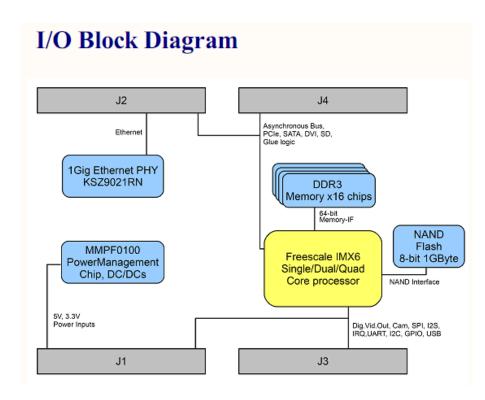

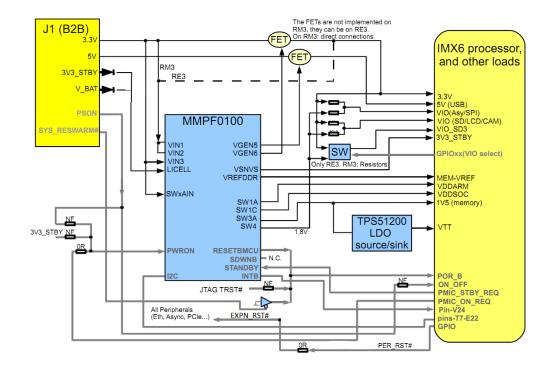

The following block diagram shows the key components of the RM3

#### **Specification**

- NXP i.MX6 ARM Cortex-A9 1GHz Dual/Quad Core Processor with TrustZone\*

- Cortex A9 NEON<sup>™</sup> MPE (Media Processing Engine) Co-Processor per Core

- 32KB Instruction Cache + 32KB Data Cache per core

- 1 MB unified I/D L2 cache, shared by two/four cores

- 1GB 64 bit DDR3 RAM

- Hardware Accelerators

- VPU Video Processing Unit

- IPUv3H Image Processing Unit version 3H (2 IPUs)

- GPU3Dv4 3D Graphics Processing Unit (OpenGLES 2.0) version 4

- GPU2Dv2 2D Graphics Processing Unit (BitBlt)

- GPUVG OpenVG 1.1 Graphics Processing Unit

- ASRC Asynchronous Sample Rate Converter

- 1GB NAND Flash

- Integrated SATA-II interface

- 1 x SPI Bus 2 devices

- 2 x UARTs

- 2 x I2S

- 2 x SD/MMC

- 1 x HS USB

- 1 x HS USB ULPI Bus

- 2 x I2C Bus

- 1 x OneWire Bus

- GPIO

- 10/100/1000 Ethernet

- PCI-E x1

- 1x 16 bit Asynchronous Bus (similar to X-Bus )

- 1 x Power LED

- Dual HD displays (DVI/HDMI & LCD) supported simultaneously and independently. Total raw pixel rate of all interfaces is up to 450Mpixels/sec, 24 bpp.

- One video camera/capture port concurrent operation with dual video channels

- 1 x Mono Channel microphone input

- 1 x Mono Channel Audio output

## **General Precautions**

Your Single Board Computer is susceptible to damage by electrostatic discharges. In order to avoid damage, you should work at an anti-static bench and observe normal anti-static precautions. Wear an anti-static wrist strap connected to an earth point *before* opening any packaging.

Where a wrist strap is not available, discharge any static charge you may have built-up by touching an earth point. Avoid any further movement that could build up another static charge. Touch an earth point from time to time to avoid further build-up, and remove the items from their anti-static bags only when required

#### **Electro-Static Discharges**

If you are going to open up the unit, it is important to realise that the devices on the cards within this unit can be damaged by static electricity. Bear in mind that the damage caused by static electricity may vary from total destruction to partial damage, which may not be immediately obvious. This could have an effect on the product's reliability and warranty. Before opening the chassis, ensure that you take necessary static precautions. Ideally you should work at an anti-static bench and wear an approved wrist strap or if that is not possible, touch a suitable ground to discharge any static build up before touching the electronics. This should be repeated if the handling continues for any length of time.

If it is necessary to remove a board or electronic assembly, place it into an anti-static bag. This will prevent any static electricity build up damaging the board. Metallised bags are preferred. Do not use black anti-static bags for any item containing a battery because these tend to be conductive and will discharge the battery.

# **Mechanical Specifications**

#### **Outline Dimensions**

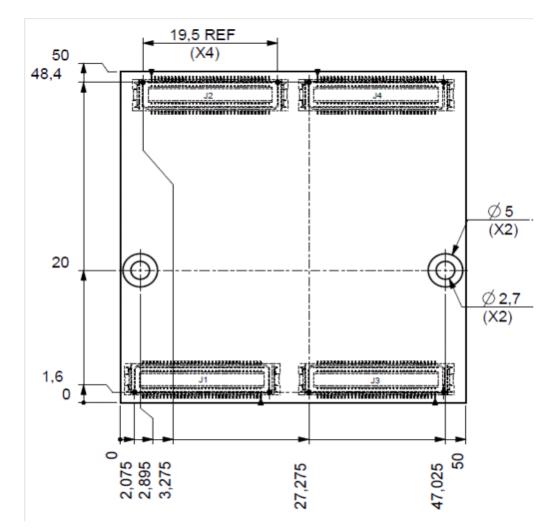

Notes:-

- 1. The above shows the position of the SOM mounting sockets and outline of the SOM module as seen from the top of the PCB/host board

- 2. Pin 1 position is 'rotational': it appears top-left of sockets J2 & J4 as shown, and bottom-right of sockets J1 & J3 sockets

- 3. Polarity is ensured by the difference in spacing of the LH & RH socket pairs: it is not possible to fit the PCB incorrectly

- 4. The SOM PCB should be secured in place with two mount-pillars (shown)

- 5. The connectors on the SOM module are 70-pin Hirose DF17-3.0-70DS-0.5 connectors. **The mating half required on the hostboard would be the Hirose DF17-XX-70DP-0.5** where XX can be 2.0 or 2.5 or 4.0 which specifies the stacking height adjustment. With the DF17-2.0-70DS-0.5 the baseboard adds 2mm to the SOM module's 3mm to create a 5mm stacking height (between PCBs). Similarly the DF17-2.5-70DS-0.5 will create a 5.5mm stacking height; the DF17-4.0-70DS-0.5 would create a 7mm stacking height. For a 5mm stack height a suitable M2.5, 5mm spacer would be Farnell p/n 1467010

N.B For thermal reasons, it is recommended that active devices are not placed beneath the module on the host/carrier board

## **Connector Details**

In the following pin summaries, currently 'reserved' pins are greyed out. Host boards should not make connections to these pins without first consulting with Blue Chip Technology. Not all RMx SOM PCBs support all of the defined pins.

| 11    |                |    |    |            |        |

|-------|----------------|----|----|------------|--------|

| LCD   | LCD_ENA        | 2  | 1  | GND        | CAMERA |

| CNTRL | LCD_BL_ENA     | 4  | 3  | CAM_D13    |        |

|       | GND            | 6  | 5  | CAM_D12    |        |

| USB   | USB_HOST_P     | 8  | 7  | CAM_D11    |        |

| HOST  | USB_HOST_N     | 10 | 9  | CAM_D10    |        |

|       | GND            | 12 | 11 | CAM_D9     |        |

|       | USB_DEV_P      | 14 | 13 | CAM_D8     |        |

|       | USB_DEV_N      | 16 | 15 | CAM_D7     |        |

|       | GND            | 18 | 17 | CAM_D6     |        |

| POWER | VCC5           | 20 | 19 | GND        |        |

|       | VIO            | 22 | 21 | CAM_D5     |        |

|       | VIO            | 24 | 23 | CAM_D4     |        |

| TV    | GND            | 26 | 25 | CAM_D3     |        |

|       | TV_LUMA_COMP   | 28 | 27 | CAM_D2     |        |

|       | GND            | 30 | 29 | CAM_D1     |        |

|       | TV_CHROMA      | 32 | 31 | CAM_D0     |        |

|       | GND            | 34 | 33 | GND        |        |

| LCD   | LCD_PWMB       | 36 | 35 | CAM_STROBE |        |

| PWM   | LCD_PWMA       | 38 | 37 | CAM_WEN    |        |

|       | GND            | 40 | 39 | CAM_FLD    |        |

| AUDIO | AUD_LINEIN_L   | 42 | 41 | CAM_HS     |        |

|       | AUD_LINEIN_R   | 44 | 43 | CAM_VS     |        |

|       | AUD_MICIN_BIAS | 46 | 45 | GND        |        |

|       | AUD_MICIN_N    | 48 | 47 | CAM_PCLK   |        |

|       | AUD_MICIN_P    | 50 | 49 | GND        |        |

|       | GND            | 52 | 51 | CAM_XCLKB  |        |

|       | AUD_LINEOUT_R  | 54 | 53 | CAM_XCLKA  |        |

|       | AUD_LINEOUT_L  | 56 | 55 | GND        |        |

11

#### RM3

#### **Specifications**

| GND       | 58 57 | CAM_GLOBAL_RESET |       |

|-----------|-------|------------------|-------|

| IIS_DX    | 60 59 | GND              |       |

| IIS_DR    | 62 61 | 3V3_SBY          | POWER |

| IIS_CLKX  | 64 63 | VCC3_3           |       |

| IIS_FSX   | 66 65 | VCC3_3           |       |

| AUDIORSTN | 68 67 | VCC3_3           |       |

| GND       | 70 69 | VCC3_3           |       |

| - 7 |

|-----|

|     |

|     |

| 12   |              |    |    |              |      |

|------|--------------|----|----|--------------|------|

| LAN  | GND          | 2  | 1  | GND          |      |

|      | ETH_TX2_P    | 4  | 3  | EXPN_CEO#    |      |

|      | ETH_TX2_N    | 6  | 5  | EXPN_CE1#    |      |

|      | GND          | 8  | 7  | GND          | SATA |

|      | ETH_RX2_P    | 10 | 9  | SATA_RX_N    |      |

|      | ETH_RX2_N    | 12 | 11 | SATA_RX_P    |      |

|      | GND          | 14 | 13 | GND          |      |

|      | ETH_TX1_P    | 16 | 15 | SATA_TX_N    |      |

|      | ETH_TX1_N    | 18 | 17 | SATA_TX_N    |      |

|      | GND          | 20 | 19 | GND          | DVI  |

|      | ETH_RX1_P    | 22 | 21 | DVI_C_N      |      |

|      | ETH_RX1_N    | 24 | 23 | DVI_C_P      |      |

|      | GND          | 26 | 25 | GND          |      |

|      | ETH_SPD_LED# | 28 | 27 | DVI_D2_N     |      |

|      | ETH_LNK_LED# | 30 | 29 | DVI_D2_N     | _    |

|      | ETH_CTT      | 32 | 31 | GND          |      |

|      | GND          | 34 | 33 | DVI_D1_N     |      |

| BUS  | EXPN_WP#     | 36 | 35 | DVI_D1_P     |      |

| EXPN | EXPN_CE4#    | 38 | 37 | GND          |      |

|      | EXPN_WE#     | 40 | 39 | DVI_D0_N     |      |

|      | EXPN_RE#     | 42 | 41 | DVI_D0_P     |      |

|      | EXPN_ALE     | 44 | 43 | GND          |      |

|      | EXPN_A11     | 46 | 45 | CEC          |      |

|      | EXPN_READY   | 48 | 47 | DVI_HPD      |      |

|      | EXPN_A7      | 50 | 49 | GND          |      |

|      | EXPN_A6      | 52 | 51 | PCIE_CLK_P   | PCIe |

|      | EXPN_A5      | 54 | 53 | PCIE_CLK_N   | _    |

|      | EXPN_A4      | 56 | 55 | GND          |      |

|      | EXPN_A3      | 58 | 57 | PCIE_TX_P    |      |

|      | EXPN_A2      | 60 | 59 | PCIE_TX_N    | _    |

|      | EXPN_A1      | 62 | 61 | GND          |      |

|      | EXPN_D15     | 64 | 63 | PCIE_RX_P    |      |

|      | EXPN_D14     | 66 | 65 | PCIE_RX_N    |      |

|      | EXPN_D13     | 68 | 67 | GND          |      |

|      | GND          | 70 | 69 | USB_DEV_VBUS |      |

| 13  |           | r     |            |          |

|-----|-----------|-------|------------|----------|

| LCD | GND       | 2 1   | GND        | CAMERA   |

|     | LCD_D14   | 4 3   | CAM_D14    |          |

|     | LCD_D15   | 6 5   | CAM_D15    |          |

|     | GND       | 8 7   | GND        |          |

|     | LCD_D16   | 10 9  | CAN_1      | SLOW     |

|     | LCD_D17   | 12 11 | CAN_2      | SERIAL   |

|     | LCD_D18   | 14 13 | CAN_3      |          |

|     | LCD_D19   | 16 15 | UARTA_TX   |          |

|     | LCD_D20   | 18 17 | UARTB_TX   |          |

|     | LCD_D21   | 20 19 | UARTA_ENTX |          |

|     | GND       | 22 21 | UARTA_RX   |          |

|     | LCD_D22   | 24 23 | UARTB_RX   |          |

|     | LCD_D23   | 26 25 | GND        |          |

|     | LCD_PCLK  | 28 27 | SPI_CLK    |          |

|     | GND       | 30 29 | SPI_CSB    |          |

|     | LCD_HSYNC | 32 31 | SPI_SIMO   |          |

|     | LCD_VSYNC | 34 33 | SPI_SOMI   |          |

|     | LCD_DE    | 36 35 | SPI_CSA    |          |

|     | LCD_D0    | 38 37 | SOM_IRQA#  | INTERRPT |

|     | LCD_D1    | 40 39 | SOM_IRQB#  |          |

|     | LCD_D2    | 42 41 | GND        |          |

|     | LCD_D3    | 44 43 | I2CA_SCL   | I2C      |

|     | GND       | 46 45 | I2CA_SDA   |          |

|     | LCD_D4    | 48 47 | I2CB_SCL   |          |

|     | LCD_D5    | 50 49 | I2CB_SDA   |          |

|     | LCD_D6    | 52 51 | GPIO1      | GPIO     |

|     | LCD_D7    | 54 53 | GPIO2      |          |

|     | LCD_D8    | 56 55 | GPIO3      |          |

|     | LCD_D9    | 58 57 | GPIO4      |          |

|     | GND       | 60 59 | GND        |          |

|     | LCD_D10   | 62 61 | GPIO5      |          |

|     | LCD_D11   | 64 63 | GPIO6      |          |

|     | LCD_D12   | 66 65 | GPIO7      |          |

|     | LCD_D13   | 68 67 | GPIO8      |          |

|     | GND       | 70 69 | GND        |          |

| J4          |                 |    |    |           |        |

|-------------|-----------------|----|----|-----------|--------|

|             | GND             | 2  | 1  | GND       |        |

| BUS         | EXPN_FLASH_SEL  | 4  | 3  |           |        |

| EXPN        | EXPN_D12        | 6  | 5  |           |        |

| [Continued] | EXPN_D11        | 8  | 7  |           |        |

|             | EXPN_D10        | 10 | 9  | GND       |        |

|             | EXPN_D9         | 12 | 11 |           |        |

|             | EXPN_D8         | 14 | 13 |           |        |

|             | EXPN_D7         | 16 | 15 |           |        |

|             | EXPN_D6         | 18 | 17 |           |        |

|             | EXPN_D5         | 20 | 19 |           |        |

|             | EXPN_D4         | 22 | 21 | GND       |        |

|             | EXPN_D3         | 24 | 23 |           |        |

|             | EXPN_D2         | 26 | 25 |           |        |

|             | EXPN_D1         | 28 | 27 |           |        |

|             | EXPN_D0         | 30 | 29 |           |        |

|             | GND             | 32 | 31 |           |        |

| MISC        | HDQ             | 34 | 33 |           |        |

|             | PSON            | 36 | 35 |           |        |

|             | SYS_RES#        | 38 | 37 |           |        |

|             | WAKEUP#         | 40 | 39 | GND       |        |

|             | EXPN_CLE        | 42 | 41 | SD2_DATA0 | SD/MMC |

|             | BOOT_MODE#      | 44 | 43 | SD2_DATA1 |        |

|             | CAM_IRQ         | 46 | 45 | SD2_DATA2 |        |

|             | BT_PWR_EN       | 48 | 47 | SD2_DATA3 |        |

|             | SOM_IRQC#       | 50 | 49 | SD2_CMD   |        |

|             | WIRELESS_PWR_EN | 52 | 51 | SD2_CLK   |        |

|             | EXPN_RESET#     | 54 | 53 | GND       |        |

|             | VBATT           | 56 | 55 | VSD1      |        |

|             | SD1_WP          | 58 | 57 | SD1_SDCD  |        |

|             | GND             | 60 | 59 | SD1_DATA0 |        |

|             |                 | 62 | 61 | SD1_DATA1 |        |

|             |                 | 64 | 63 | SD1_DATA2 |        |

|             |                 | 66 | 65 | SD1_DATA3 |        |

|             |                 | 68 | 67 | SD1_CMD   |        |

|             | GND             | 70 | 69 | SD1_CLK   |        |

The following is an outline of some of the Signals on the SOM which relate in particular to the RM3. For a fuller list please refer to the SOM Specification Guide.

| Power   | Pin   | Power Rail  | Description:                             |

|---------|-------|-------------|------------------------------------------|

|         | Type: | /Tolerance: |                                          |

| VCC3_3  | PWR   | 3.3V        | Power feed for SOM                       |

| 3V3_SBY | PWR   | 3.3V        | Standby power feed for SOM               |

| VIO     | PWR   | 1.8V(typ)   | Power reference from SOM                 |

|         |       | 3.3V (max)  |                                          |

| VCC5    | PWR   | 5V          | Power feed for SOM                       |

| VBATT   | PWR   | 1.8V-3.3V   | Nom 3V (1.8V-3.3V) DC power feed for SOM |

|         |       |             | RTC                                      |

| GND     | PWR   | 0V          | Power/signal ground                      |

VIO is a reference supply provided by the RM3 SOM to identify the configured logic level for a number of interfaces. For flexible support of RMx SOMs, this should be used to define the SOM side of a level-shifter for affected circuits. It is possible to operate without a level-shifter if a host platform is designed for a specific RMx SOM (in which case the I/O voltage can be designed against that provided in the specific RMx documentation). The presence of VIO should be used to enable power to the peripherals on the host board in order to prevent phantom powering and failure to initialise correctly.

3V3\_SBY is required, and should always be present whenever the other main supplies (VCC5 & VCC3\_3) are available.

#### **Power Sequence**

3V3\_SBY must be present when VCC\_3\_3 is present. Both may be applied at the same instant (same source) VIO is a reference supply for level shifters and power control on the host board

Leakage voltages are prevented by use of VIO to enable power to the peripherals on the host board. This can be achieved by enable/disable of a power supply or by a switch activated by VIO. A typical example of this is using a MIC94040 or MIC94042 for soft-start.

#### **Power Consumption**

The power consumed by RM3 varies greatly depending on what the module is doing.

For example, CPU loading affects power consumption, and so does the graphics accelerator and video accelerator.

The table below shows the current and power for various common scenarios:

| Activity                               | Current @ 3.3V | Power |

|----------------------------------------|----------------|-------|

| CPU idle                               | 0.61A          | 2.0W  |

| CPU 100%                               | 0.96A          | 3.2W  |

| CPU idle + VPU (video decode 800x600)  | 0.80A          | 2.6W  |

| CPU idle + VPU (video decode 1080p)    | 0.85A          | 2.8W  |

| CPU 100% + VPU (800x600)               | 1.24A          | 4.1W  |

| CPU 100% + GPU (1080p) + VPU (800x600) | 1.96A          | 6.5W  |

All figures are taken from a quad-core RM3 running Ubuntu 11.10 with HDMI output at 1080p@60fps and LCD output at 800x600@60fps.

Typical current for other supplies:

#### **Power Supply Current**

3.3V Standby < 10mA 5V < 20mA

Provision of VBATT is optional (note that maintaining the RTC in power down may not be possible if this supply is not available). Typical drain in powered-off mode is around 7.5uA

All directions below are given with respect to the host/carrier board (ie: 'O' or 'Output' is a signal from the host board to the SOM).

| Digital Display #1<br>(Parallel/LCD) | Host Pin<br>Type: | Power Rail<br>/Tolerance: | Description:                      |

|--------------------------------------|-------------------|---------------------------|-----------------------------------|

|                                      | Type.             |                           |                                   |

| LCD_D0                               | 1                 | VIO                       | 24-bit parallel display interface |

| LCD_D23                              | 1                 |                           |                                   |

| LCD_HSYNC                            | 1                 |                           | Horizontal synchronisation        |

| LCD_VSYNC                            | 1                 |                           | Vertical synchronisation          |

| LCD_PCLK                             | 1                 |                           |                                   |

| LCD_DE                               | 1                 |                           |                                   |

| LCD_ENA                              | 1                 | VIO                       | Enable/disable panel              |

| LCD_BL_ENA                           | 1                 |                           | Enable/disable backlight          |

| PWM Output | Host Pin<br>Type: | Power Rail<br>/Tolerance: | Description:                 |

|------------|-------------------|---------------------------|------------------------------|

| LCD_PWMA   | I                 | 3.3V                      | Pulse-width modulator output |

| LCD_PWMB   | I                 |                           | Pulse-width modulator output |

[If not required for brightness/contrast control, the PWM outputs can be used as general-purpose PWM outputs].

The LCD interface is designed for simple connection of panels offering a basic, parallel interface. Backlight/inverter power should be provided by the host PCB.

## **Slow Serial Interfaces**

| CAN   | Host Pin<br>Type: | Power Rail<br>/Tolerance: | Description:     |

|-------|-------------------|---------------------------|------------------|

| CAN_1 | 0                 | 3.3V                      | RX (to SOM)      |

| CAN_2 | 1                 |                           | TX (from SOM)    |

| CAN_3 | 1                 |                           | TX_EN (from SOM) |

The CAN transceiver is implemented on the host PCB when required.

| UART A     | Host Pin<br>Type: | Power Rail<br>/Tolerance: | Description:            |

|------------|-------------------|---------------------------|-------------------------|

| UARTA_TX   | I                 | 3.3V                      | Serial transmit         |

| UARTA_ENTX | I                 |                           | Transmit enable control |

| UARTA_RX   | 0                 |                           | Serial receive          |

| UART B   | Host Pin<br>Type: | Power Rail<br>/Tolerance: | Description:    |

|----------|-------------------|---------------------------|-----------------|

| UARTB_TX | 1                 | 3.3V                      | Serial transmit |

| UARTB_RX | 0                 |                           | Serial receive  |

Two, simple, two-wire UART interfaces are provided at basic logic level. UARTA adds a transmit enable signal to simplify use on multi-drop buses (eg: RS485) where disabling/tri-stating of the transceiver is required. Handshaking and access control, if desired, should be implemented at the software level (eg: using 'XON/XOFF').

UARTB is the default debug serial port. It is recommended that this be made available (as a minimum as contactable pads, or a pin header interface) on host boards.

| SPI      | Host<br>PinType: | Power Rail<br>/Tolerance: | Description: |

|----------|------------------|---------------------------|--------------|

| SPI_CLK  | 1                | 3.3V                      |              |

| SPI_CSB  | 1                |                           |              |

| SPI_SIMO | 1                |                           |              |

| SPI_SOMI | 0                |                           |              |

| SPI_CSA  | 1                |                           |              |

The Serial Peripheral Interface bus provided by the SOM operates with the SOM as master, and up to two slave addresses attached (selected using SPI\_CSA & SPI\_CSB) operating in independent mode. Note that – if two devices are used on this bus, both must be capable of operating in multi-slave environments (ie: must support 'slave select' signalling and tri-state outputs when not addressed).

# **I<sup>2</sup>C Interfaces**

| ŕc       | Host Pin<br>Type: | Power Rail<br>/Tolerance: | Description: |

|----------|-------------------|---------------------------|--------------|

| I2CA_SCL | I/O               | 5V                        |              |

| I2CA_SDA | I/O               | 5V                        |              |

| I2CB_SCL | I/O               | 3.3V                      |              |

| I2CB_SDA | I/O               | 3.3V                      |              |

I2CA is the default for use as a DDC channel for a display interface (see later).

#### **GPIO**

| GPIO   | RMx System<br>On Module | Power Rail<br>/Tolerance: | Description:                |

|--------|-------------------------|---------------------------|-----------------------------|

|        | Specification*:         |                           |                             |

| GPIO1  | 1                       | 3.3V                      | General purpose I/O signals |

| GPIO2  | 1                       |                           |                             |

| GPIO3  | 1                       |                           |                             |

| GPIO4  | 1                       |                           |                             |

| GPIO5  | 0                       |                           |                             |

| GPIO6  | 0                       |                           |                             |

| GPIO7  | 0                       |                           |                             |

| GPIO8  | 0                       |                           |                             |

| GPIO9  | 1                       |                           |                             |

| GPIO10 | 0                       |                           |                             |

\*The direction of each GPIO interface indicated above is as defined by the RMx System On Module Specification and is supported by all RMx SOMs. The GPIO directions in the RMx System On Module Specification are defined as fixed direction, however in the case of RM3 all GPIO signals are directly attached to the i.MX6 system on chip and can be controlled as either inputs or outputs under software control.

### <u>USB</u>

| USB Device   | Host Pin           | Power Rail  | Description:                         |

|--------------|--------------------|-------------|--------------------------------------|

|              | Туре:              | /Tolerance: |                                      |

| USB_DEV_P/N  | I/O <sub>BAL</sub> |             | Standard balanced USB bi-directional |

|              |                    |             | signal data bus                      |

| USB_DEV_VBUS | А                  | 5V          | Used to determine mode (*1)          |

| USB_OTG_ID   | 0                  | 5V          | Standard USB OTG ID signal           |

[Note \*1: The 'USB\_DEV\_VBUS' signal on the USB device interface is fed to the SOM to indicate presence of a suitable USB 'host' on the link].

The USB Device port is a principal interface for configuration of SOM modules. It is recommended that it be made available (at least as contactable pads, or a pin header) on host boards.

The "device" port may also support OTG functionality on some modules.

| USB Host #1  | Host Pin<br>Type:  | Power Rail<br>/Tolerance: | Description:                                            |

|--------------|--------------------|---------------------------|---------------------------------------------------------|

| USB_HOST_P/N | I/O <sub>BAL</sub> |                           | Standard balanced USB bi-directional<br>signal data bus |

### <u>Audio</u>

| Digital Audio | Host Pin | Power Rail  | Description:                       |

|---------------|----------|-------------|------------------------------------|

|               | Туре:    | /Tolerance: |                                    |

| AUDIORSTN     | 1        | VIO         | Reset signal for host audio codecs |

| IIS_FSX       | 1        | VIO         | Framing for output channel         |

| IIS_CLKX      | 1        | VIO         | Transmit/receive clock             |

| IIS_DR        | 0        | VIO         | Receive data                       |

| IIS_DX        | 1        | VIO         | Transmit data                      |

| Analogue Audio | Host Pin       | Power Rail  | Description:                          |

|----------------|----------------|-------------|---------------------------------------|

|                | Туре:          | /Tolerance: |                                       |

| AUD_LINEOUT_L  | I <sub>A</sub> | 3.3V        | Left & right channel analogue signals |

| AUD_LINEOUT_R  | I <sub>A</sub> | 3.3V        |                                       |

|                |                |             |                                       |

| AUD_MICIN_P    | O <sub>A</sub> | 3.3V        | Balanced microphone analogue signal   |

| AUD_MICIN_N    | O <sub>A</sub> | 3.3V        |                                       |

| AUD_MICIN_BIAS | I <sub>A</sub> | 3.3V        |                                       |

|                |                |             |                                       |

| AUD_LINEIN_L   | O <sub>A</sub> | 3.3V        | Left line input ('mono in' for RM2)   |

| AUD_LINEIN_R   | O <sub>A</sub> | 3.3V        | Right line input                      |

RM3 supports either digital or analogue audio. Selection is under software control. The 'AUDIORSTN' signal will be permanently active from RM3 whilst software selection is of the on-board codec (thus holding any host-board codec in hard-reset until it is enabled to avoid possible contention on the I2C & IIS buses).

The analogue audio channel provides signal levels typically up to 0dBu (0.775V rms).

AUD\_MICIN\_BIAS is a configurable, low-voltage bias voltage to power suitable microphones

| Digital Video In #1 | Host Pin | Power Rail  | Description:               |

|---------------------|----------|-------------|----------------------------|

|                     | Туре:    | /Tolerance: |                            |

| CAM_GLOBAL_RESET    | Ι        | VIO         |                            |

| CAM_PCLK            | 0        | VIO         | Pixel clock                |

| CAM_VS              | 0        | VIO         | Vertical Sync              |

| CAM_HS              | 0        | VIO         | Horizontal Sync            |

| CAM_WEN             | Ι        | VIO         | Enable camera function     |

| CAM_D0 - CAM_D9     | 0        | VIO         | 10-bit parallel data       |

| CAM_XD0 - CAM_XD1   | 0        | VIO         | Function depends on module |

| CAM_XD2 - CAM_XD5   | 0        | VIO         | []                         |

### Video/Camera Interfaces

The primary Digital Video Input #1 is designed for connection of cameras and similar devices to the SOM.

For maximum compatibility across modules it is recommended to use one of the following configurations:

- ITU-R BT.656 mode with 10-bit parallel data and embedded sync

- SYNC mode with 10-bit parallel data and separate Horizontal Sync and Vertical Sync

Other configurations are available, depending on which module is being used - see appendices for more information.

## **LAN/Ethernet**

| Ethernet     | Host Pin | Power Rail  | Description:                            |

|--------------|----------|-------------|-----------------------------------------|

|              | Туре:    | /Tolerance: |                                         |

| ETH_SPD_LED# | I        | 3.3V        | Open drain driver for "Speed" LED       |

| ETH_LNK_LED# | 1        | 3.3V        | Open drain driver for "Link" LED        |

| ETH_CTT      | А        |             | Centre-tap connection from magnetics    |

| ETH_TX1_P/N  | BAL      |             | Transmit pair for 10/100Base-T          |

| ETH_RX1_P/N  | BAL      |             | Receive pair for 10/100Base-T           |

| ETH_TX2_P/N  | BAL      |             | 5 · · · · · · · · · · · · · · · · · · · |

| ETH_RX2_P/N  | BAL      |             | Extra pairs for 1000Base-T              |

All SOMs support a basic 10/100Base-T Ethernet configuration; some support Gigabit Ethernet.

The PHY is implemented on the SOM; magnetics and connectorisation are required on the host board

#### **SATA**

| SATA                       | Host Pin<br>Type:                    | Power Rail<br>/Tolerance: | Description: |

|----------------------------|--------------------------------------|---------------------------|--------------|

| SATA_RX_P/N<br>SATA_TX_P/N | O <sub>BAL</sub><br>I <sub>BAL</sub> |                           |              |

### **DVI/HDMI**

| Digital Display #2 | Host Pin         | Power Rail  | Description:                         |

|--------------------|------------------|-------------|--------------------------------------|

| (DVI/HDMI)         | Туре:            | /Tolerance: |                                      |

| HDMI_C_P/N         | I <sub>BAL</sub> | 3.3V        | DVI-I (HDMI 1.4a support may also be |

| HDMI_D0_P/N        | I <sub>BAL</sub> |             | available) interface                 |

| HDMI_D1_P/N        | I <sub>BAL</sub> |             |                                      |

| HDMI_D2_P/N        | I <sub>BAL</sub> |             |                                      |

| HDMI_HPD           | 0                | 3.3V        | Hot Plug Detect signal from attached |

|                    |                  |             | displays                             |

| CEC                | I/O              | 3.3V        | 'Consumer Electronics Control'       |

|                    |                  |             | channel (for HDMI implementations)   |

Digital display #2 offers DVI-SL, and may optionally offer HDMI interface support<sup>1</sup>.

If a DDC channel is required, I2CA should be used.

## **PCle**

| PCI Express (x1) | Host Pin<br>Type: | Power Rail<br>/Tolerance: | Description:                          |

|------------------|-------------------|---------------------------|---------------------------------------|

| PCIE_CLK_P/N     | I <sub>BAL</sub>  | 3.3V                      | Single-channel PCI express interface  |

| PCIE_TX_P/N      | I <sub>BAL</sub>  |                           | with reference clock (for any devices |

| PCIE_RX_P/N      | O <sub>BAL</sub>  |                           | requiring this feature)               |

<sup>&</sup>lt;sup>1</sup> HDMI support may be subject to licensing

### **SDIO/SD/MMC**

These ports provide connectivity to SD/MMC memory, or to SDIO devices (such as wireless modules).

| SD/MMC/SDIO #1 | Host Pin | Power Rail  | Description:                          |

|----------------|----------|-------------|---------------------------------------|

|                | Туре:    | /Tolerance: |                                       |

| SD1_WP         | 0        | VSD1        | Port for connection of flash memory   |

| SD1_CD         | 0        | 3.3V        | devices or SDIO communication         |

| SD1_DATA0      | I/O      | VSD1        | devices.                              |

| SD1_DATA1      | I/O      | VSD1        | VSD1 is a voltage output from the SOM |

| SD1_DATA2      | I/O      | VSD1        | to define and provide the I/O power   |

| SD1_DATA3      | I/O      | VSD1        | for the interface. It can be also be  |

| SD1_CMD        | I/O      | VSD1        | turned off & on by the SOM to         |

| SD1_CLK        | 1        | VSD1        | shutdown attached devices or provide  |

| VSD1           | А        | [Note *1]   | a hard reset.                         |

Note \*1: VSD1 is sourced from the SOM and provides power for SD1-connected devices and the reference voltage for any associated pull-up resistors. VSD1 is sourced from the 3.3V rail of the SOM.

| SD/MMC/SDIO #2 | Host Pin<br>Type: | Power Rail<br>/Tolerance: | Description:                          |

|----------------|-------------------|---------------------------|---------------------------------------|

| SD2_DATA0      | I/O               | 3.3V                      | Port for connection of flash memory   |

| SD2_DATA1      | I/O               |                           | devices or SDIO communication         |

| SD2_DATA2      | I/O               |                           | devices. Note that voltage selection, |

| SD2_DATA3      | I/O               |                           | card-detection, and write-protect     |

| SD2_CMD        | I/O               |                           | features are not available for this   |

| SD2_CLK        | 1                 |                           | interface                             |

#### **Key Notes for Compatibility**

SD1 is primarily designed for use with SD/MMC/SDIO devices. All RMx modules support 4-bit SD/SDIO/MMC cards operating at 'higher' voltage levels (typically 2.7V to 3.6V); not all RMx modules support switching to lower voltage mode (1.7V to 1.95V), but all support power cycling to enable card reset. Mechanical 'Write Protect' is not supported by all RMx cards. RM3 **only** supports 3.3V operation.

SD2 is available for SD/MMC/SDIO type devices, but does not support any power control features or mechanical card detect/write protect. It is more appropriate for use as an interface to embedded devices on the host board.

For maximum compatibility, SD/SDIO or uSD devices are recommended.

The power supply should be decoupled at the card slot to minimise hot-insertion transients. Values of 47uF for SD cards and 100uF for SDIO cards are recommended.

### **Expansion Bus**

| Expansion Bus | Host Pin | Power Rail  | Description:                          |

|---------------|----------|-------------|---------------------------------------|

|               | Туре:    | /Tolerance: |                                       |

| EXPN_A11      | 1        | VIO         |                                       |

| EXPN_A7       | 1        |             |                                       |

| EXPN_A6       | 1        |             |                                       |

| EXPN_A5       | 1        |             |                                       |

| EXPN_A4       | 1        |             |                                       |

| EXPN_A3       | I        |             |                                       |

| EXPN_A2       | 1        |             |                                       |

| EXPN_A1       | I        |             |                                       |

| EXPN_D15      | I/O      |             | 16-bit wide data bus                  |

| EXPN_D14      | I/O      |             |                                       |

| EXPN_D13      | I/O      |             |                                       |

| EXPN_D12      | I/O      |             |                                       |

| EXPN_D11      | I/O      |             |                                       |

| EXPN_D10      | I/O      |             |                                       |

| EXPN_D9       | I/O      |             |                                       |

| EXPN_D8       | I/O      |             |                                       |

| EXPN_D7       | I/O      |             |                                       |

| EXPN_D6       | I/O      |             |                                       |

| EXPN_D5       | I/O      |             |                                       |

| EXPN_D4       | I/O      |             |                                       |

| EXPN_D3       | I/O      |             |                                       |

| EXPN_D2       | I/O      |             |                                       |

| EXPN_D1       | I/O      |             |                                       |

| EXPN_D0       | I/O      |             |                                       |

| EXPN_CE0#     | 1        |             | Three available chip-select signals.  |

| EXPN_CE1#     | 1        |             | Note that some RMx modules may        |

| EXPN_CE4#     | 1        |             | have restrictions on the use of these |

| EXPN_WE#      | 1        |             | Data write strobe                     |

| EXPN_RE#      | 1        |             | Data read strobe                      |

| EXPN_READY    | 0        |             |                                       |

| EXPN_RESET#   | 1        |             | Can be used as a generic system reset |

The expansion bus is provided as a flexible interface to memory-mapped host-board resources. The range available may vary dependent on RMx module in use, however there is some overlap in support.

Simple non-multiplexed devices (eg: suitably-configured FPGAs) with PSRAM/NOR flash like interfaces can be supported in order to implement specialised interface functionality.

### **Miscellaneous**

|                                                | Host<br>Pin<br>Type: | Power Rail<br>/Tolerance:        | Description:                                                                                                                                 | Availability:                            |

|------------------------------------------------|----------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| PSON                                           | 1                    | 3.3V                             | Control wire from SOM<br>0 = Power off<br>1 = Power on                                                                                       | None - no<br>longer used                 |

| SYS_RES#                                       | 0                    | [Use OD<br>driver <sup>2</sup> ] | Reset signal into SOM<br>0 = Reset RMx<br>1 = Normal operation                                                                               | RM2/RM3                                  |

| WAKEUP#                                        | 0                    | [Use OD<br>driver]               | 'Wake' signal into SOM<br>0 = wake from sleep state<br>1 = [no change in state]                                                              | RM2/RM3                                  |

| BOOT_MODE#                                     | 0                    | 3.3V                             | [See below]                                                                                                                                  | RM2/RM3                                  |

| WIRELESS_PWR_EN3V                              | I                    | 3.3V                             | Control wire from SOM<br>0 = Disable WLAN<br>1 = Enable WLAN                                                                                 | RM2/RM3                                  |

| SOM_IRQA#<br>SOM_IRQB#<br>SOM_IRQC#<br>CAM_IRQ | 0<br>0<br>0<br>0     | VIO                              | Interrupt lines to SOM. 'CAM_IRQ' is<br>dedicated to the primary digital video<br>input. Pull up to VIO using 10K resistors<br>on host board | RM2/RM3<br>RM2/RM3<br>RM2/RM3<br>RM2/RM3 |

| EXPN_FLASH_SEL                                 | 0                    | 3.3V                             | [See below]                                                                                                                                  | RM3                                      |

It is recommended that miscellaneous output pins should use open-drain drivers on the host, tolerant to 5V, in order to ensure full compatibility with all RMx modules. In practice, it is unlikely that these interfaces will be presented with more than 3.3V.

| Signal:        | Description:                                                                                                                                                                                                 |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOOT_MODE#     | Normal (not connected): RMx boot controlled by EXPN_FLASH_SEL.<br>Tied to GND: Force boot from USB (serial loader)                                                                                           |

| EXPN_FLASH_SEL | [Only effective if BOOT_MODE# is not connected]<br>This pin is reserved for Blue Chip Technology use, and customers are<br>advised to leave the pin floating (standard boot is from on-card Flash<br>memory) |

The above signals are pulled-up on the RMx (see the relevant Appendix for details), and so do not need to be pulled high on the host board in order to set a 'high' level.

BOOT\_MODE# is a dual-purpose signal intended to enable:-

- Boot from alternative interface to enable initial program/re-program of the on-SOM Flash memory

- Entry into 'engineering mode' (depending on bootloader/operating system) to enable reconfiguration of operating modes of the SOM

The former is triggered if the signal is active at power-up; the latter function is reliant on using a suitable bootloader, and is entered dependant on a software test of the same signal some time after initial power-up.

<sup>&</sup>lt;sup>2</sup> Signal is pulled up on SOM (may be to any supply between 1.8V and 5V)

# **Cooling**

Efficient cooling is essential for long and reliable operation of any electronic equipment, and the RM3 SOM is no different. While able to operate in a local ambient up to  $+60^{\circ}$ C/ $+85^{\circ}$ C (depending on processor type and cooling solution) continued long term operation at higher temperatures will reduce the life of components and ultimately the SOM itself. Therefore it is beneficial to try and keep the local ambient as low as possible. When laying out a Hostboard design, care should be taken to avoid placing heat generating components underneath the SOM.

The +60/85°C operation is the ambient temperature close to the RM3 SOM. If the SOM is placed in a small enclosure then this "local" ambient is likely to be higher than the room ambient outside the enclosure. When choosing or designing the enclosure, care should be taken to try and minimise the temperature rise inside the enclosure over the room ambient.

At the prototype design stage it is advisable to attach thermal probes close to the SOM and at other points inside the enclosure [for instance close to heat generating components on the Hostboard] to determine the temperature difference local to the SOM in comparison with the ambient outside the enclosure.

To aid design, there is a temperature sensor on the i.MX6 chip which can be read from the Linux shell. The sensor has a file system interface, so the temperature can be obtained by reading the relevant file

#### cat /sys/class/thermal/thermal\_zone0/temp

The following script can be used to get a temperature reading printed once every second (press CTRL+C to stop):

#### while true; do cat /sys/class/thermal/thermal\_zone0/temp; sleep 1; done;

Where the temperature difference is high and the expected maximum working room (or free air) ambient is also high, then additional cooling arrangements may be required to keep the local ambient close to the SOM below its maximum value. For instance this could be achieved via extra ventilation holes in the enclosure, fitment of a fan, fitment of a larger heatsink or even a combination of all 3.

# **System Software**

### **Operating Systems Supported**

Ubuntu 14.04 LTS

Yocto 2.1 (Krogoth)

Android 4.4.3

For Linux the RM3 is supplied with a U-Boot bootloader installed in SPI NOR Flash. Source code and demonstration Operating System images are available but it is intended that customers will develop their own image suited to their particular application. Refer to the relevant Blue Chip Technology Operating System Guide for the RM3.

Note that in order to change or adjust U-Boot settings, a Serial interface (UARTB) is required.

# **Maintenance**

The RM3 SOM module should not require any regular maintenance.

## **History**

| Issue Level | Issue Date | Author  | Amendment Details                                                                                                              |

|-------------|------------|---------|--------------------------------------------------------------------------------------------------------------------------------|

| 1.0         | Nov 2013   | Various | 1 <sup>st</sup> release                                                                                                        |

| 1.1         | June 2016  | нıт     | Updated to include 1GB as standard, revised part<br>number to match the new website, OS update plus<br>general clarifications. |

| 1.2         | July 2016  | BH      | Corrections made to the direction of the Expansion bus<br>Addresses, CEx, WE,RE and RESET signals                              |

| 1.3         | Nov 2016   | TGH     | Re-corrected the Expansion bus directions; clarified<br>SYS_RES, PSON, VSD1; added power-up sequence                           |

| 1.4         | July 2017  | DR      | Clarified directions of GPIO signals in relation to the RMx System On Module Specification                                     |

#### Contact Details Blue Chip Technology Ltd. Chowley Oak Tattenhall Chester CH3 9EX U.K. Telephone: +44 (0)1829 772000 Facsimile: +44 (0)1829 772001

www.bluechiptechnology.com

The Support email address requires the sender to be first registered on the Support Web site at

http://support.bluechiptechnology.co.uk/

To request a Returns Authorisation number, please use the RMA portal at

Http://rma.bluechiptechnology.co.uk